Tool/software:

Hi,

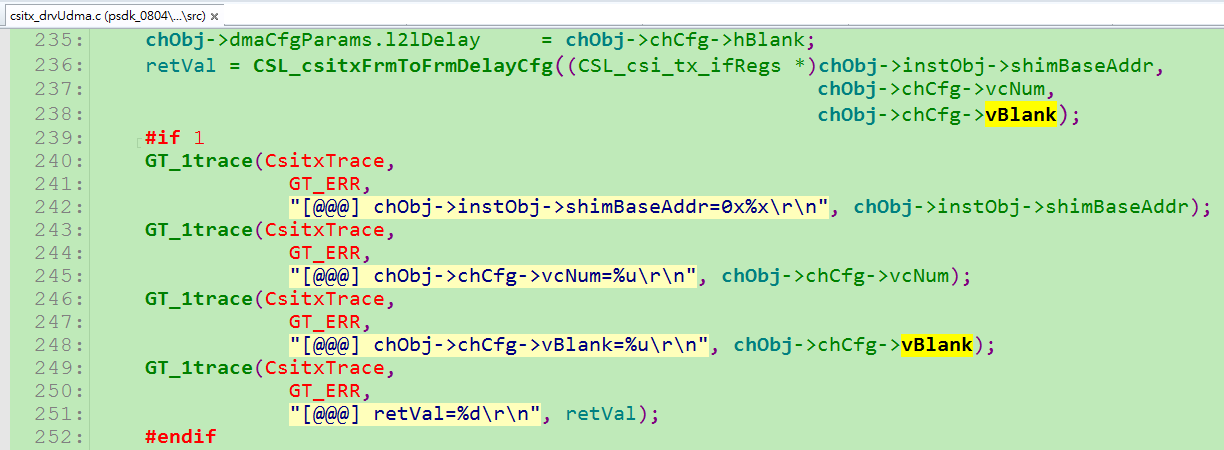

We used psdk_0804.

//

j7_csitx.h

uint32_t vBlank; /*!< Vertical blanking in terms of number of line. */

//

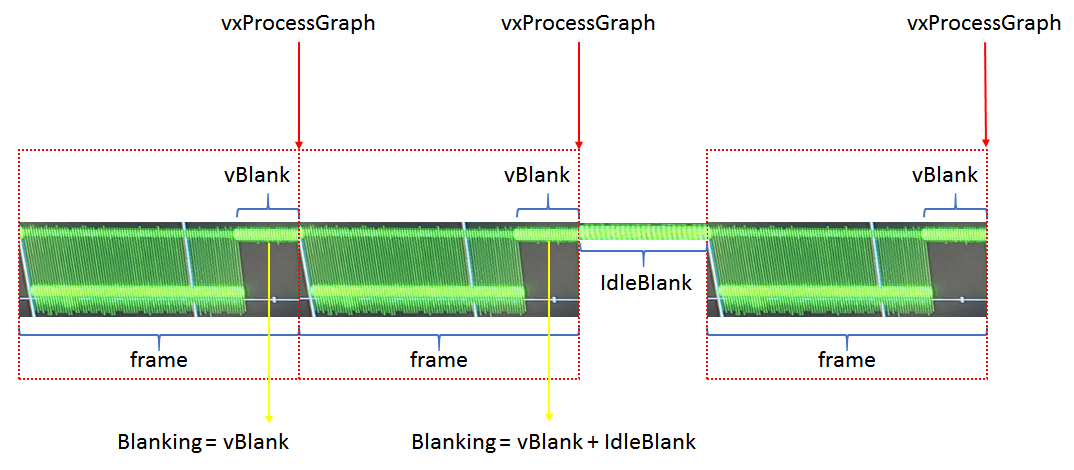

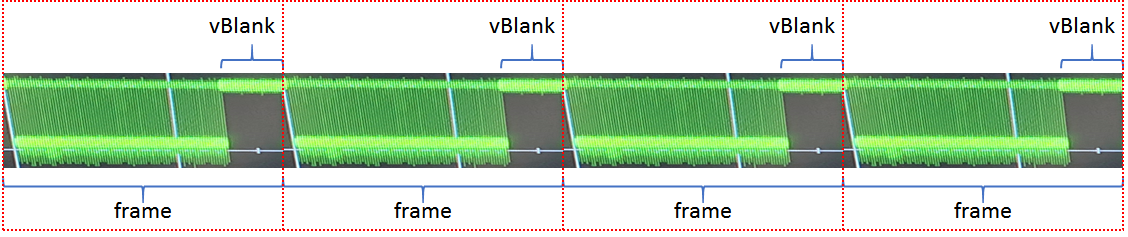

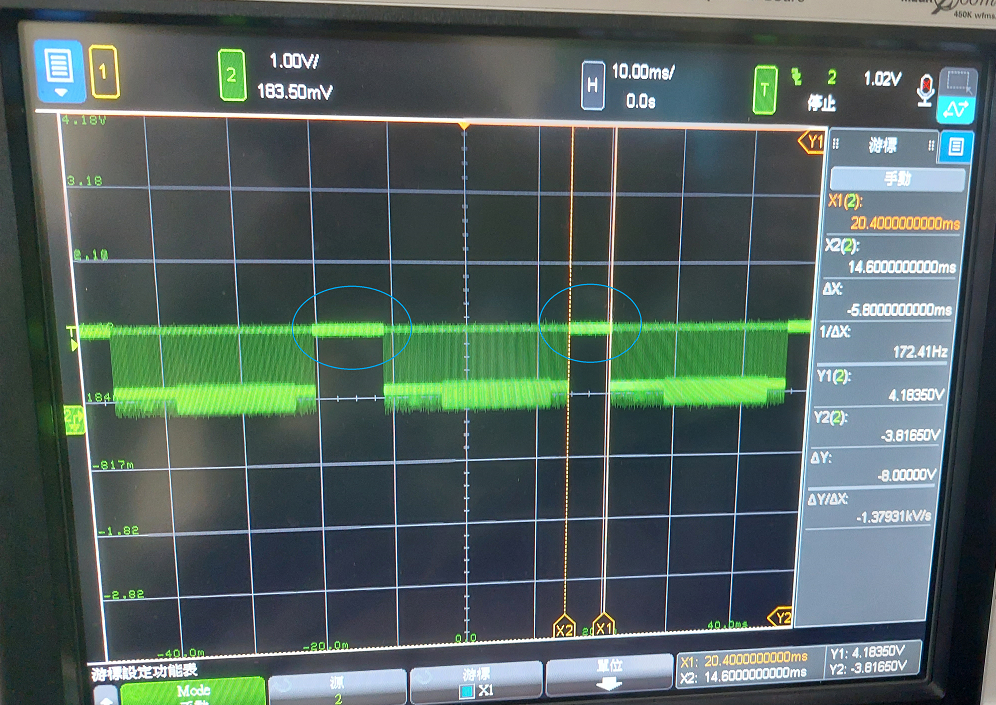

We think the blanking should be a fixed value when set vBlank.

But the blanking is not fixed as below.

Is "blanking config of csitx node" work ?

How could we set the blanking ?

Regards,