Tool/software:

Hi,

We want to optimize DDR memory layout for TDA4.

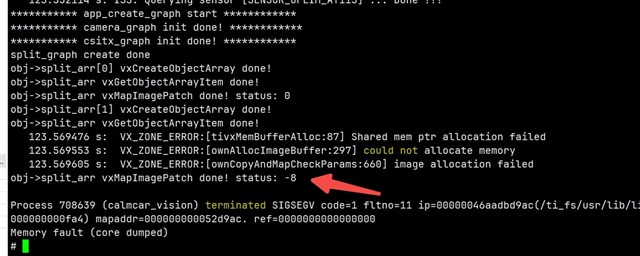

After reducing size of SHMEM, the Shared memory for Buffers/ION allocator, there is a vxMapImagePatch fail said that shared mem ptr allocation failed.

We want to know that for VX_ZONE how to calculate the appropriate shared memory size for a camera of resolution 1280x1285.

<!DOCTYPE html>

<html>

<style type="text/css">

.tg {border-collapse:collapse;border-spacing:0;border-color:#999;}

.tg td{font-family:Arial, sans-serif;font-size:14px;padding:10px 5px;border-style:solid;border-width:1px;overflow:hidden;word-break:normal;border-color:#999;color:#444;background-color:#F7FDFA;}

.tg th{font-family:Arial, sans-serif;font-size:14px;font-weight:normal;padding:10px 5px;border-style:solid;border-width:1px;overflow:hidden;word-break:normal;border-color:#999;color:#fff;background-color:#26ADE4;}

.tg .tg-kftd{background-color:#efefef;text-align:left;vertical-align:top}

.tg .tg-6sgx{background-color:#ffffff;text-align:left;vertical-align:top}

.tg .tg-fjir{background-color:#343434;color:#ffffff;text-align:left;vertical-align:top}

</style>

<head>

<title>System Memory Map for Linux+RTOS mode</title>

</head>

<body>

<h1>System Memory Map for Linux+RTOS mode</h1>

<p>Note, this file is auto generated using PyTI_PSDK_RTOS tool</p>

<table class="tg">

<tr>

<th class="tg-fjir">Name</th>

<th class="tg-fjir">Start Addr</th>

<th class="tg-fjir">End Addr</th>

<th class="tg-fjir">Size </th>

<th class="tg-fjir">Attributes</th>

<th class="tg-fjir">Description</th>

</tr>

<tr>

<td class="tg-kftd">L2RAM_C66x_1</td>

<td class="tg-kftd">0x00800000</td>

<td class="tg-kftd">0x00837FFF</td>

<td class="tg-kftd">224.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">L2 for C66x_1</td>

</tr>

<tr>

<td class="tg-6sgx">L2RAM_C66x_2</td>

<td class="tg-6sgx">0x00800000</td>

<td class="tg-6sgx">0x00837FFF</td>

<td class="tg-6sgx">224.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">L2 for C66x_2</td>

</tr>

<tr>

<td class="tg-kftd">MAIN_OCRAM_MCU2_0</td>

<td class="tg-kftd">0x03600000</td>

<td class="tg-kftd">0x0361FFFF</td>

<td class="tg-kftd">128.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">Main OCRAM for MCU2_0</td>

</tr>

<tr>

<td class="tg-6sgx">MAIN_OCRAM_MCU2_1</td>

<td class="tg-6sgx">0x03620000</td>

<td class="tg-6sgx">0x0363FFFF</td>

<td class="tg-6sgx">128.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">Main OCRAM for MCU2_1</td>

</tr>

<tr>

<td class="tg-kftd">L2RAM_C7x_1</td>

<td class="tg-kftd">0x64800000</td>

<td class="tg-kftd">0x64877FFF</td>

<td class="tg-kftd">480.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">L2 for C7x_1</td>

</tr>

<tr>

<td class="tg-6sgx">L1RAM_C7x_1</td>

<td class="tg-6sgx">0x64E00000</td>

<td class="tg-6sgx">0x64E03FFF</td>

<td class="tg-6sgx">16.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">L1 for C7x_1</td>

</tr>

<tr>

<td class="tg-kftd">MSMC_MPU1</td>

<td class="tg-kftd">0x70000000</td>

<td class="tg-kftd">0x7001FFFF</td>

<td class="tg-kftd">128.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">MSMC reserved for MPU1 for ATF</td>

</tr>

<tr>

<td class="tg-6sgx">MSMC_C7x_1</td>

<td class="tg-6sgx">0x70020000</td>

<td class="tg-6sgx">0x707E7FFF</td>

<td class="tg-6sgx"> 7.78 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">MSMC for C7x_1</td>

</tr>

<tr>

<td class="tg-kftd">MSMC_DMSC</td>

<td class="tg-kftd">0x707F0000</td>

<td class="tg-kftd">0x707FFFFF</td>

<td class="tg-kftd">64.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">MSMC reserved for DMSC IPC</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU1_0_IPC</td>

<td class="tg-6sgx">0x95100000</td>

<td class="tg-6sgx">0x951FFFFF</td>

<td class="tg-6sgx">1024.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU1_0 for Linux IPC</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU1_0_RESOURCE_TABLE</td>

<td class="tg-kftd">0x95200000</td>

<td class="tg-kftd">0x952003FF</td>

<td class="tg-kftd">1024 B</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU1_0 for Linux resource table</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU1_0</td>

<td class="tg-6sgx">0x95200400</td>

<td class="tg-6sgx">0x963FFFFF</td>

<td class="tg-6sgx">18.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU1_0 for code/data</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU1_1_IPC</td>

<td class="tg-kftd">0x96400000</td>

<td class="tg-kftd">0x964FFFFF</td>

<td class="tg-kftd">1024.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU1_1 for Linux IPC</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU1_1_RESOURCE_TABLE</td>

<td class="tg-6sgx">0x96500000</td>

<td class="tg-6sgx">0x965003FF</td>

<td class="tg-6sgx">1024 B</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU1_1 for Linux resource table</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU1_1</td>

<td class="tg-kftd">0x96500400</td>

<td class="tg-kftd">0x976FFFFF</td>

<td class="tg-kftd">18.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU1_1 for code/data</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU2_0_IPC</td>

<td class="tg-6sgx">0x97700000</td>

<td class="tg-6sgx">0x977FFFFF</td>

<td class="tg-6sgx">1024.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_0 for Linux IPC</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU2_0_RESOURCE_TABLE</td>

<td class="tg-kftd">0x97800000</td>

<td class="tg-kftd">0x978003FF</td>

<td class="tg-kftd">1024 B</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_0 for Linux resource table</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU2_0</td>

<td class="tg-6sgx">0x97800400</td>

<td class="tg-6sgx">0x996FFFFF</td>

<td class="tg-6sgx">31.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_0 for code/data</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU2_1_IPC</td>

<td class="tg-kftd">0x99700000</td>

<td class="tg-kftd">0x997FFFFF</td>

<td class="tg-kftd">1024.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_1 for Linux IPC</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU2_1_RESOURCE_TABLE</td>

<td class="tg-6sgx">0x99800000</td>

<td class="tg-6sgx">0x998003FF</td>

<td class="tg-6sgx">1024 B</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_1 for Linux resource table</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU2_1</td>

<td class="tg-kftd">0x99800400</td>

<td class="tg-kftd">0x9B6FFFFF</td>

<td class="tg-kftd">31.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_1 for code/data</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU3_0_IPC</td>

<td class="tg-6sgx">0x9B700000</td>

<td class="tg-6sgx">0x9B7FFFFF</td>

<td class="tg-6sgx">1024.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU3_0 for Linux IPC</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU3_0_RESOURCE_TABLE</td>

<td class="tg-kftd">0x9B800000</td>

<td class="tg-kftd">0x9B8003FF</td>

<td class="tg-kftd">1024 B</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU3_0 for Linux resource table</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU3_0</td>

<td class="tg-6sgx">0x9B800400</td>

<td class="tg-6sgx">0x9DFFFFFF</td>

<td class="tg-6sgx">40.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU3_0 for code/data</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU3_1_IPC</td>

<td class="tg-kftd">0x9E000000</td>

<td class="tg-kftd">0x9E0FFFFF</td>

<td class="tg-kftd">1024.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU3_1 for Linux IPC</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU3_1_RESOURCE_TABLE</td>

<td class="tg-6sgx">0x9E100000</td>

<td class="tg-6sgx">0x9E1003FF</td>

<td class="tg-6sgx">1024 B</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU3_1 for Linux resource table</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU3_1</td>

<td class="tg-kftd">0x9E100400</td>

<td class="tg-kftd">0x9EFFFFFF</td>

<td class="tg-kftd">15.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU3_1 for code/data</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_C7x_1_IPC</td>

<td class="tg-6sgx">0x9F000000</td>

<td class="tg-6sgx">0x9F0FFFFF</td>

<td class="tg-6sgx">1024.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for C7x_1 for Linux IPC</td>

</tr>

<tr>

<td class="tg-kftd">DDR_C7x_1_RESOURCE_TABLE</td>

<td class="tg-kftd">0x9F100000</td>

<td class="tg-kftd">0x9F1003FF</td>

<td class="tg-kftd">1024 B</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for C7x_1 for Linux resource table</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_C7x_1_BOOT</td>

<td class="tg-6sgx">0x9F200000</td>

<td class="tg-6sgx">0x9F2003FF</td>

<td class="tg-6sgx">1024 B</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for C7x_1 for boot section</td>

</tr>

<tr>

<td class="tg-kftd">DDR_C7x_1_VECS</td>

<td class="tg-kftd">0x9F400000</td>

<td class="tg-kftd">0x9F403FFF</td>

<td class="tg-kftd">16.00 KB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for C7x_1 for vecs section</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_C7x_1_SECURE_VECS</td>

<td class="tg-6sgx">0x9F600000</td>

<td class="tg-6sgx">0x9F603FFF</td>

<td class="tg-6sgx">16.00 KB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for C7x_1 for secure vecs section</td>

</tr>

<tr>

<td class="tg-kftd">DDR_C7x_1</td>

<td class="tg-kftd">0x9F604000</td>

<td class="tg-kftd">0xA3FFFFFF</td>

<td class="tg-kftd">73.98 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for C7x_1 for code/data</td>

</tr>

<tr>

<td class="tg-6sgx">TIOVX_LOG_RT_MEM</td>

<td class="tg-6sgx">0xA4000000</td>

<td class="tg-6sgx">0xA5FFFFFF</td>

<td class="tg-6sgx">32.00 MB</td>

<td class="tg-6sgx"></td>

<td class="tg-6sgx">Memory for TI OpenVX shared memory for Run-time logging. MUST be non-cached or cache-coherent</td>

</tr>

<tr>

<td class="tg-kftd">IPC_VRING_MEM</td>

<td class="tg-kftd">0xA7000000</td>

<td class="tg-kftd">0xA8FFFFFF</td>

<td class="tg-kftd">32.00 MB</td>

<td class="tg-kftd"></td>

<td class="tg-kftd">Memory for IPC Vring's. MUST be non-cached or cache-coherent</td>

</tr>

<tr>

<td class="tg-6sgx">APP_LOG_MEM</td>

<td class="tg-6sgx">0xA9000000</td>

<td class="tg-6sgx">0xA903FFFF</td>

<td class="tg-6sgx">256.00 KB</td>

<td class="tg-6sgx"></td>

<td class="tg-6sgx">Memory for remote core logging</td>

</tr>

<tr>

<td class="tg-kftd">TIOVX_OBJ_DESC_MEM</td>

<td class="tg-kftd">0xA9040000</td>

<td class="tg-kftd">0xACFDFFFF</td>

<td class="tg-kftd">63.62 MB</td>

<td class="tg-kftd"></td>

<td class="tg-kftd">Memory for TI OpenVX shared memory. MUST be non-cached or cache-coherent</td>

</tr>

<tr>

<td class="tg-6sgx">PCIE_QUEUE_SHARED_MEM</td>

<td class="tg-6sgx">0xACFE0000</td>

<td class="tg-6sgx">0xACFEFFFF</td>

<td class="tg-6sgx">64.00 KB</td>

<td class="tg-6sgx"></td>

<td class="tg-6sgx">Memory for IPC over PCIe using shared memory. MUST be non-cached or cache-coherent</td>

</tr>

<tr>

<td class="tg-kftd">PCIE_QUEUE_MIRROR_REMOTE_SHARED_MEM</td>

<td class="tg-kftd">0xACFF0000</td>

<td class="tg-kftd">0xACFFFFFF</td>

<td class="tg-kftd">64.00 KB</td>

<td class="tg-kftd"></td>

<td class="tg-kftd">Reserved Memory for RAT mapping of remote PCIe IPC shared memory. MUST be non-cached or cache-coherent</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_SHARED_MEM</td>

<td class="tg-6sgx">0xAD000000</td>

<td class="tg-6sgx">0xB2FFFFFF</td>

<td class="tg-6sgx">96.00 MB</td>

<td class="tg-6sgx"></td>

<td class="tg-6sgx">Memory for shared memory buffers in DDR</td>

</tr>

<tr>

<td class="tg-kftd">DDR_SHARED_MEM_BSW</td>

<td class="tg-kftd">0xD3000000</td>

<td class="tg-kftd">0xD4FFFFFF</td>

<td class="tg-kftd">32.00 MB</td>

<td class="tg-kftd"></td>

<td class="tg-kftd">Memory for shared memory buffers in DDR, BSW shared memory</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU2_0_NON_CACHE</td>

<td class="tg-6sgx">0xD5000000</td>

<td class="tg-6sgx">0xD5FFFFFF</td>

<td class="tg-6sgx">16.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_0 for non-cached heap</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU2_0_LOCAL_HEAP</td>

<td class="tg-kftd">0xD6000000</td>

<td class="tg-kftd">0xD6FFFFFF</td>

<td class="tg-kftd">16.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_0 for local heap</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU2_1_NON_CACHE</td>

<td class="tg-6sgx">0xD7000000</td>

<td class="tg-6sgx">0xDDFFFFFF</td>

<td class="tg-6sgx">112.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU2_1 for non-cached heap</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU1_0_LOCAL_HEAP</td>

<td class="tg-kftd">0xDE000000</td>

<td class="tg-kftd">0xDE7FFFFF</td>

<td class="tg-kftd"> 8.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU1_0 for local heap</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU1_1_LOCAL_HEAP</td>

<td class="tg-6sgx">0xDE800000</td>

<td class="tg-6sgx">0xDEFFFFFF</td>

<td class="tg-6sgx"> 8.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU1_1 for local heap</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU2_1_LOCAL_HEAP</td>

<td class="tg-kftd">0xDF000000</td>

<td class="tg-kftd">0xDFFFFFFF</td>

<td class="tg-kftd">16.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU2_1 for local heap</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_MCU3_0_LOCAL_HEAP</td>

<td class="tg-6sgx">0xE0000000</td>

<td class="tg-6sgx">0xE07FFFFF</td>

<td class="tg-6sgx"> 8.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for MCU3_0 for local heap</td>

</tr>

<tr>

<td class="tg-kftd">DDR_MCU3_1_LOCAL_HEAP</td>

<td class="tg-kftd">0xE0800000</td>

<td class="tg-kftd">0xE0FFFFFF</td>

<td class="tg-kftd"> 8.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for MCU3_1 for local heap</td>

</tr>

<tr>

<td class="tg-6sgx">DDR_C7X_1_SCRATCH</td>

<td class="tg-6sgx">0xE1000000</td>

<td class="tg-6sgx">0xE6FFFFFF</td>

<td class="tg-6sgx">96.00 MB</td>

<td class="tg-6sgx">RWIX</td>

<td class="tg-6sgx">DDR for c7x_1 for Scratch Memory</td>

</tr>

<tr>

<td class="tg-kftd">DDR_C7X_1_LOCAL_HEAP</td>

<td class="tg-kftd">0x100000000</td>

<td class="tg-kftd">0x105FFFFFF</td>

<td class="tg-kftd">96.00 MB</td>

<td class="tg-kftd">RWIX</td>

<td class="tg-kftd">DDR for c7x_1 for local heap</td>

</tr>

</table>

</body>

</html>