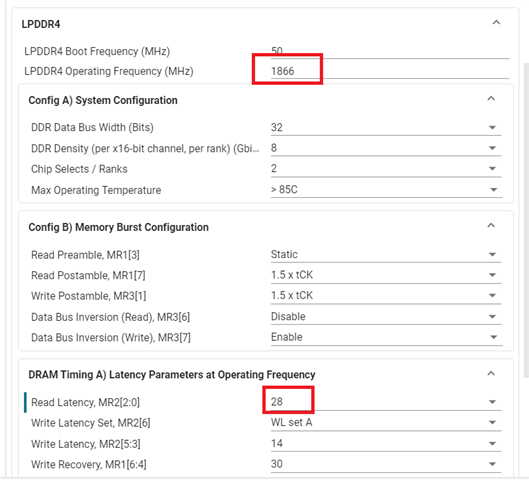

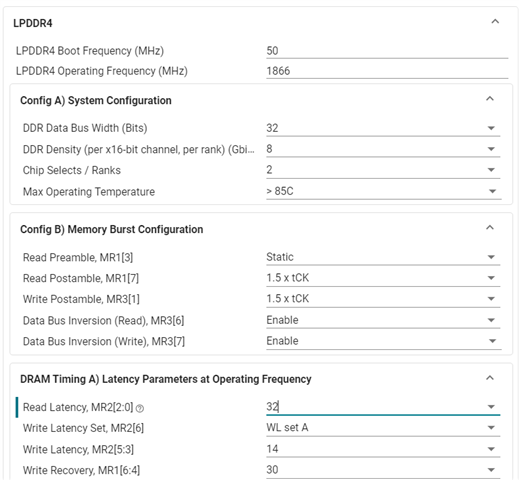

Part Number: TDA4VEN-Q1

Tool/software:

Hi TI's experts,

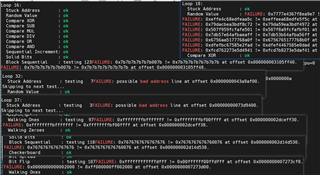

We are debugging the HLX LPDDR4(32Gb H54G56BYYVX046) in our own TDA4Ven board,there are some failures when I doing the memtester.

Can you help me figure out what the problem is?

memtester result:

Regards.