Tool/software:

Hi Support Team,

Our customer has reported the following failure.

[Failure Overview]

App: Monitoring Monitor

Circumstance:

-Monitoring monitor to get a waveform is connected to the main monitor via a wired LAN and monitored centrally on the main monitor.

In this case, there is a problem that the waveform on the main monitor is interrupted between 0.5s and 10s.

-There was no problem with the Ethernet's transmitted waveform, and the transmission was never stopped from the host side.

-When the transmission waveform was interrupted, the PHY (LAN8710AI) inside the monitoring monitor was softly reset.

-The results of the evaluation revealed that when the transmission waveform was interrupted,

the PHY (LAN8710AI) inside the monitoring monitor was soft reset.

-When we checked the cause of this reset, we found that it was due to a missing or unrecognized packet

in the received packet.

-We checked the waveforms of Ether and RMII, and did not find any significant missing waveforms

in Ether and RMII before the reset was issued.

(Waveform quality could not be confirmed because the waveforms were observed

while the device was embedded in the equipment.)

-This model has been mass-produced for about 10 years and there had been no problem until now,

However, 6 out of 10 units manufactured in 2023 and 13 out of 20 units manufactured

in the most recent period had initial defects in the form of defective boards.

-We are currently investigating the cause of the problem, but based on the results of the current investigation,

we believe that there may be some kind of failure in the RMII receiving side circuit of the AM1808 EMAC.

The details are described following.

Results of our investigation:

On this board, a damping resistor is placed near the RMII_MHZ_50_CLK (pin W18) of AM1808.

When the constant of this damping resistor is 10Ω, the problem occurs,

but when it is changed to 0Ω or 22Ω, the problem does not occur.

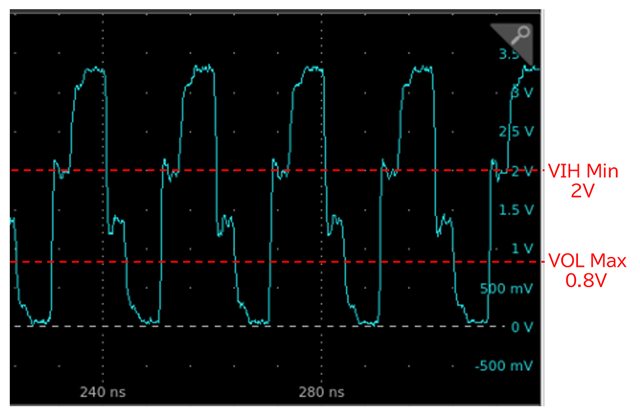

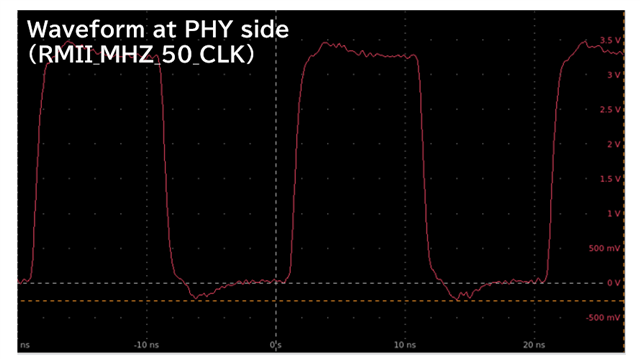

Waveforms of RMII_MHZ_50_CLK:

The waveforms were observed on the transmitter side (near the AM1808 W18 pin) and are therefore stepped.

The waveform observed at the receiving side (LAN8710AI) has no problem including setup/hold time.

RMII_MHZ_50_CLK is an input/output pin. If the waveform is stepped or

the transition time is 5ns or more (0.25P or more), is there a possibility that

a through-current flows through the input buffer at intermediate potentials, causing a problem?

We would appreciate it if you could point out any other points of concern.

Best Regards,

Kanae