- Hi Team.

- 1、Currently, we plan to use AM4372BZDNA60 and FPGA to build a hardware system.

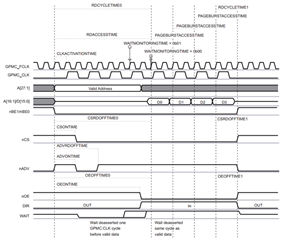

Use the GPMC interface of the CPU (AM4372) to connect to NOR FLASH and communicate with the FPGA in a non-address data line multiplexing mode, with a maximum data bit of 16 bits.

Transmit 8 data, 4 bytes each, using GPMC's DMA transmission. Using 8 DMA channels for transmission,Is this plan feasible? - 2、what is the maximum data transmission speed of DMA? What is the maximum FIFO buffer of each channel? What is the maximum memory that DMA can access? 512kb?

- Thank you.