Tool/software:

Hi TI Experts,

Customer is working on SDK5.2.

They have a problem that will produce around running a month that will cause the system stuck, and no error log shown for analyze. We have tried our best turn on most of the debug configurations in the kernel config file, but still after half a year trying, we still do not get any information when the system stuck.

Hence, an alternative way I am thinking is to enable our internal watchdog, so that every time when the system stuck after a month, the watchdog will reset our system to keep running.

Customer also validated the watchdog function on their board by manually creating a system crash problem and make the system stuck, then after some time the watchdog will make the system reboot and run normally.

We now plan to use this solution to run a month and see if the original problem happens if we could successfully reboot the system using watchdog.

There are 3 things may need your help before we do that.

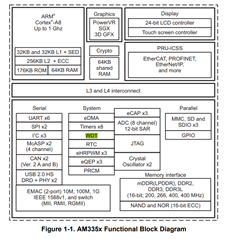

1: We see there are /dev/watchdog and /dev/watchdog0 in the coding, which one shall we use? We want to know whether watchdog or watchdog0 connects to our hardware module WDT shown below.

We want to make sure the watchdog we used actually is triggering our WDT hardware module to send the reset signal. Not like we type "reboot" command to reboot from software. So that when the problem comes we will have more chance to survive.

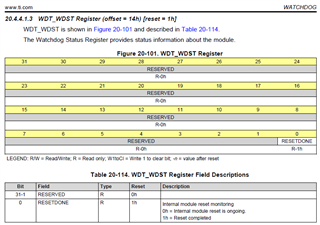

2: How do we know the reset is triggered from the watchdog, could you please provide a command to read the register so that we could know after watchdog reset?

3: Will the watchdog reset only do the warm reset or it will also trigger the PORZ?

Many Thanks,

Kevin