Tool/software:

Hi Experts,

After reading the TRM document. we understand that ECC is running internally but just for logic verification and for sil certification we require to verify the error catch in ESM.

we are using Mcu+sdk(10.00.00.14) example code.

ecc section code is avail for mcan1 we have changed to mcu msram.

Changes that we made

in ecc_init

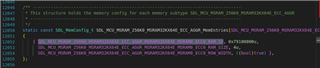

result = SDL_ECC_init(SDL_MCU_MSRAM_256K0_MSRAM32KX64E_ECC_AGGR,&ECC_Test_MCUMCAN1ECCInitConfig1); // given proper ramid as per msram

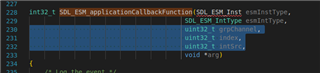

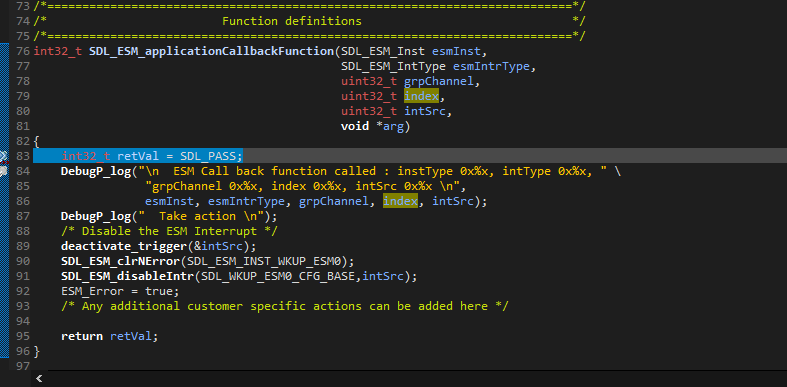

done some changes in runECC2BitMCUMCAN1_InjectTest functions

1. I can't able to found the mapping table for this address but when I search this mcan address in TRM I got in firewall region. similar I look for SRAM. can you please tell how can I get this address for each aggregator.

injectErrorConfig.pErrMem = (uint32_t *)(0x79100000u);

injectErrorConfig.flipBitMask = 0x101;

result = SDL_ECC_injectError(SDL_MCU_MSRAM_256K0_MSRAM32KX64E_ECC_AGGR,

SDL_MCU_MSRAM_256K0_MSRAM32KX64E_ECC_AGGR_MSRAM32KX64E_MSRAM0_ECC0_RAM_ID,

SDL_INJECT_ECC_ERROR_FORCING_1BIT_ONCE,

&injectErrorConfig);Output:

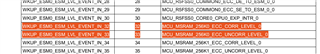

Its fail when i access bitmask = 0x101;

But its waiting for interrupt in bitmask = 0x10; but the esm module is not at all triggered.

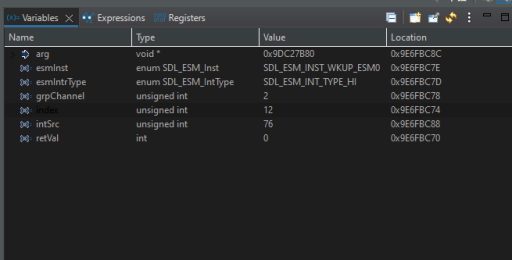

ECC Example Application ECC_Example_init: Init MAIN ESM complete ECC_Example_init: Init WKUP ESM complete ECC_init: MCU MCAN1 ECC Init complete ESM Safety Example tests: starting MCU MCAN1 Double bit error inject Example test UC-1: starting MCU MCAN1 Double bit error inject test: pError address 0x79100000 test complete and the value is 0x43F0E92D Waiting for ESM Interrupt ESM_ECC_Example_run: UC-1 has failed-1 esm error is 0... ECC Safety Example tests: failed ECC UC-1 and UC-2 Test Some Use_Cases have failed.

Can you please give me this address ranges for all this aggregators.

Regards,

Debashis