Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi,

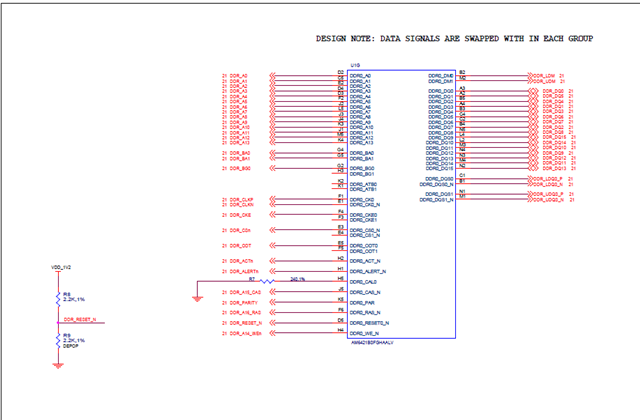

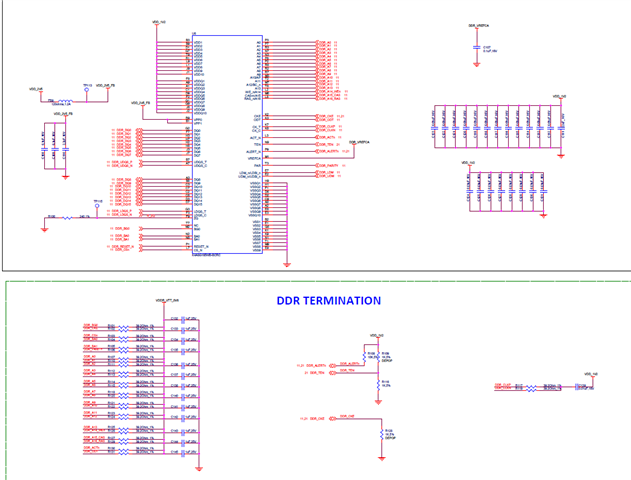

We have a custom Board with SOC AM6421 1GB K4A8G165WB-BCRC DDR.

We are using mcu_plus_sdk_am64x_09_02_00_50 SDK.

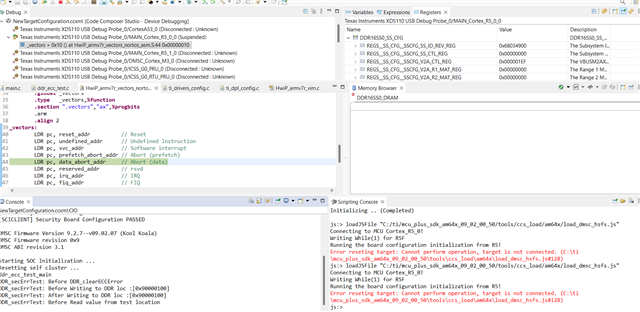

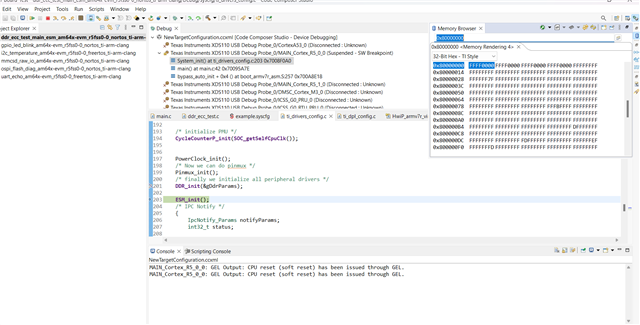

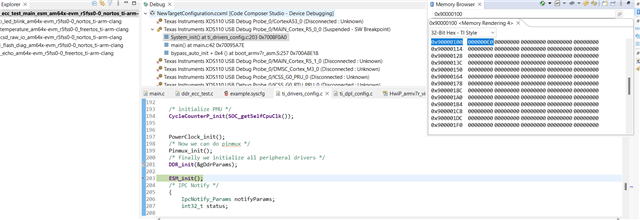

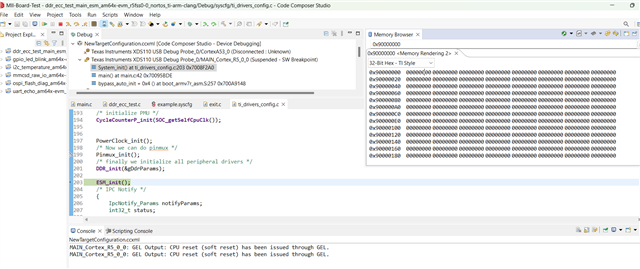

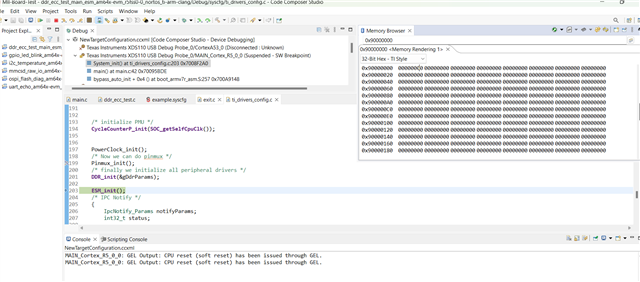

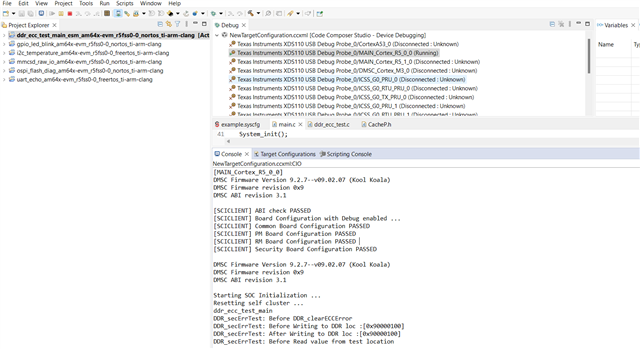

We are testing the Hardware with example ddr_ecc_test_mcu_esm from examples of SDK.

We are facing the issue

The code is as below

When running the execution stops at line

testVal = gTest_Addr[0];

Back Ground:

The same example work on our earlier Board which is 10 Layer Board and same DDR and SOC used.

Our New Board is with 12 Layer and ICCSG interface changed to MII.

We have checked the 12 layer Bare PCB Trace Lengths and track Impedance and found they are with in specified range.

Can please help us to resolve the issue.

Thank you.