Other Parts Discussed in Thread: AM62P

Tool/software:

Hi,

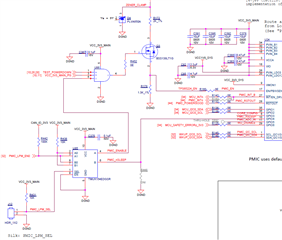

Referring to the below implementation from the SK-AM62P-LP EVK (PROC164E1-1) schematics:

1. Is it correct to assume that for supporting low power mode, should U85.1 SEL = LOW?

2. If so, in case SEL= HIGH (Low power mode is not supported), why is PMIC_LPM_EN0 connected via buffers & FET to PMIC pin 17?

Thank you for your support,

Jhon