Tool/software:

In 'u-boot', 'm trying to detect Marvell 88q2112 Phy device on TDA4AL SOC

But 'ethernet' is not found. How to fix this issue.

<Logs>

name=Marvell 88Q2112, uid=2820480, mask=268435440, phy_id=2820480

ethernet@46000000port@1 connected to Marvell 88Q2112 mode rgmii-rxid

phy_connect:1044

initQ2112Ge

_applyQ2112GeSetting

getAnegEnabled

@3. No ethernet found.

=> mdio list

mdio@f00:

ethernet@46000000port@1:

7 - Marvell 88Q2112 <--> ethernet@46000000port@1

=> mii read 0-1 0-6

Error reading from the PHY addr=00 reg=00

Error reading from the PHY addr=00 reg=01

Error reading from the PHY addr=00 reg=02

mdio read 1 1

1 is not a known ethernet

Reading from bus mdio@f00

PHY at address 1:

Error

=> mdio read 0x1 0x0900

0x1 is not a known ethernet

Reading from bus mdio@f00

PHY at address 1:

Error

</Logs>

<DTS>

aliases {

ethernet0 = &cpsw_port1;

};

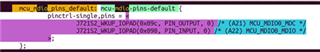

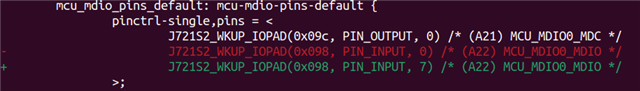

+ mcu_eth0_pins_default: mcu-eth0-pins-default {

pinctrl-single,pins = <

+ J721S2_WKUP_IOPAD(0x054, PIN_INPUT, 7) /* (E28) WKUP_GPIO0_61 ETH_SOC_INT */

+ J721S2_WKUP_IOPAD(0x050, PIN_OUTPUT, 7) /* (E27) WKUP_GPIO0_60 SOC_ETH_PHY_RESET */

>;

};

&davinci_mdio {

phy0: ethernet-phy@0 {

- reg = <0>;

+ reg = <7>; /* As per schematic */

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

ti,min-output-impedance;

+ compatible = "ethernet-phy-id002b.0980";

+ ti,dp83867-rxctrl-strap-quirk;

+ reset-assert-us = <100>;

+ reset-deassert-us = <280>;

+ reset-gpios = <&exp1 60 GPIO_ACTIVE_HIGH>;

};

};

&cpsw_port1 {

+ status = "okay";

phy-mode = "rgmii-rxid";

phy-handle = <&phy0>;

+ pinctrl-0 = <&mcu_eth0_pins_default>;

};

mcu_cpsw_pins_default: mcu-cpsw-pins-default {

pinctrl-single,pins = <

J721S2_WKUP_IOPAD(0x094, PIN_INPUT, 0) /* (B22) MCU_RGMII1_RD0 */

J721S2_WKUP_IOPAD(0x090, PIN_INPUT, 0) /* (B21) MCU_RGMII1_RD1 */

J721S2_WKUP_IOPAD(0x08c, PIN_INPUT, 0) /* (C22) MCU_RGMII1_RD2 */

J721S2_WKUP_IOPAD(0x088, PIN_INPUT, 0) /* (D23) MCU_RGMII1_RD3 */

J721S2_WKUP_IOPAD(0x084, PIN_INPUT, 0) /* (D22) MCU_RGMII1_RXC */

J721S2_WKUP_IOPAD(0x06c, PIN_INPUT, 0) /* (E23) MCU_RGMII1_RX_CTL */

J721S2_WKUP_IOPAD(0x07c, PIN_OUTPUT, 0) /* (F23) MCU_RGMII1_TD0 */

J721S2_WKUP_IOPAD(0x078, PIN_OUTPUT, 0) /* (G22) MCU_RGMII1_TD1 */

J721S2_WKUP_IOPAD(0x074, PIN_OUTPUT, 0) /* (E21) MCU_RGMII1_TD2 */

J721S2_WKUP_IOPAD(0x070, PIN_OUTPUT, 0) /* (E22) MCU_RGMII1_TD3 */

J721S2_WKUP_IOPAD(0x080, PIN_OUTPUT, 0) /* (F21) MCU_RGMII1_TXC */

J721S2_WKUP_IOPAD(0x068, PIN_OUTPUT, 0) /* (F22) MCU_RGMII1_TX_CTL */

>;

};

</DTS>