Part Number: AM6442

Tool/software:

Hi

I got an additional question to

The summary of the above is

|

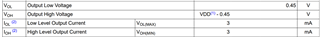

The customer is trying to use the LVCMOS output pin with 1.8VMODE, but the maximum vol value is 0.45V (IOL = 3mA), which is a high specified value, and the design does not work if the electrical characteristics are interpreted as it is.

Then I got the answer as the below. The max limit defined for VOL is valid as long as the IOL is less than 3mA, and the min limit defined for VIH is valid as long as the IOH is less than 3mA. The datasheet is saying the output buffer is able to sink current up to the min IOL current of 3mA and the low-level output voltage will remain less than the max value of 0.45V defined for VOL, and the output buffer is able to source current up to the min IOH current of 3mA and the high-level output voltage will remain greater than the min value of (VDD - 0.45V) defined for VOH. |

I understand that TI's guaranteed values are above.

How does a circuit act as a LVCMOS buffer?

If an external PD resistor or input buffer is connected and the low-side FET is turned on while AM64 is output low, will the current not drive?