Tool/software:

Hi experts,

My customer is using AM62x and wants to set OSPI Flash and OSPI Flash Boot in CCS, but there are some questions about each setting.

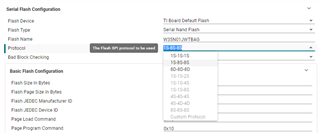

Q1. In .syscfg, Serial Flash Configuration supports three types of Protocol: "1S-1S-1S", "1S-8S-8S", and "8D-8D-8D". However, in AM62x technical reference, OSPI Boot supports "1S-1S-8S Only", and Serial NAND Boot supports "1S-1S-1S ~ 1S-1S-8S", so the only one that matches this is Serial NAND Boot's "1S-1S-1S".

Does this Protocol not have to match the Boot Protocol specification?

Should I select "1S-8S-8S" for Protocol, as per the Serial NAND Flash Boot example in SDK?

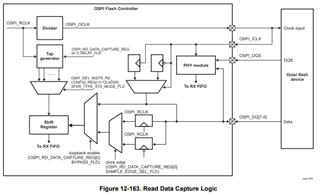

Q2. In the OSPI Driver Configuration of .syscfg, where should I refer to when setting the Input Clock Frequency (Hz) and Input Clock Divider settings? Do the settings refer to the OSPI_RCLK and Divider of the QSPI Flash Controller in the figure below?

Q3. In the Serial NAND Flash Boot example in the SDK example, the Input Clock Frequency (Hz) is "166666666" and the Input Clock Divider is "4". Why are these settings set to these values?

(Is it because the maximum clock frequency in SDR mode of the W35N01JWTBAG is 166MHz? In that case, shouldn't the settings be the OSPI_RCLK and Divider of the OSPI Flash Controller?)

Best regards,

O.H