Tool/software:

Hi TI experts!

I have a task. I have a radio frequency radar that uses the mipi (CSI2) interface and I want to run it on the J722S The interface used is CSI-Rx_IF0/dphy0. There are two challenging aspects.

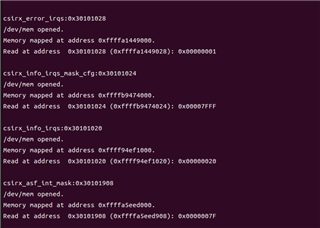

1 How can I confirm if I have received the data. Or, where is the data address of the FIFO for CSI-RX_IF0/dphy0? Can I use devmem2 to read it out and check the accuracy of the data.

2 How does the DSP retrieve and process data from a cache FIFO that is transferred to a single memory via DMA.

thanks.