Tool/software:

Hello Support Team,

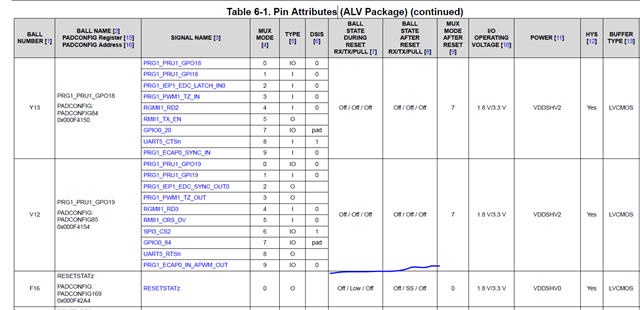

the switching characteristics of the AM64x RESETSTATz signal (Main Domain warm reset status, push-pull output) are explained in detail in the Processor Datasheet SPRSP56G,

however there is no mention about the RESETSTATz state during the power-on of the device. Even in the Technical Reference Manual SPRUIM2H I'm not able to find this information.

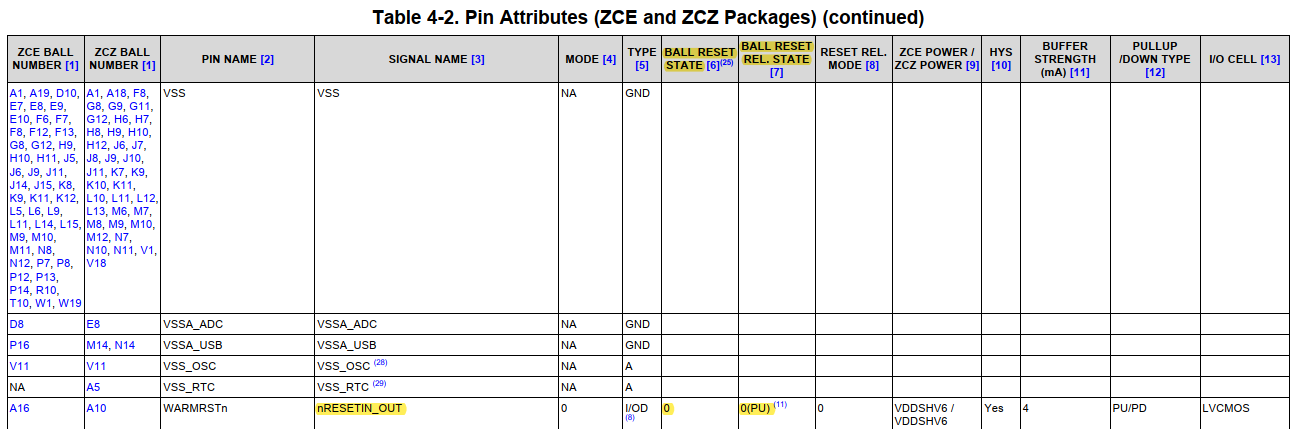

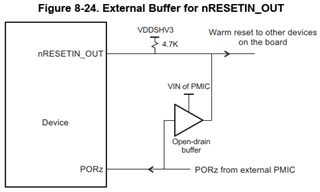

In another case, that of AM335x Sitara Processor and nRESETIN_OUT warm reset signal (input/output open drain), the Technical Reference Manual SPRUH73Q at par. 8.1.7.3.2 states that

"nRESETIN_OUT is not defined (can either be driven low or pulled up high) until all supplies are fully ramped

up. For nRESETIN_OUT to maintain a valid low state until the supples are ramped, an external buffer should be implemented, as shown in Figure 8-24."

Should I apply the same care also with the AM64x warm reset output and use an external buffer (for example, AUP buffer with 3-state output),

or is the valid low state of RESETSTATz guaranteed until the supples are fully ramped up?

Thank you in advance for your clarifications,

Kind Regards

Lorenzo