Other Parts Discussed in Thread: CDCE6214

Tool/software:

Hi everyone

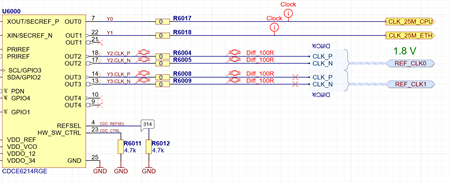

We are having technical issues with the AM6442 CPU. We use an external clockgenerator (CDCE6214) as the 100Mhz clock source for PCIe. Now we are assuming, that there is an internal pulldown resistor at the CPU side that is responsible for our problem. The clock provider is running in LP-HCSL mode and the wiring looks as follows:

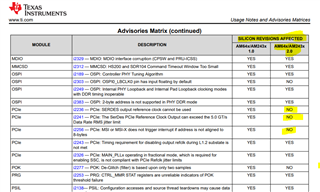

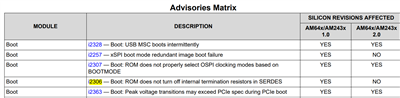

According to the errata sheet https://www.ti.com/lit/er/sprz457h/sprz457h.pdf the SERDES Output reference clock cannot be used (i2236).

Another reason is also i2241: PCIe: The SerDes PCIe Reference Clock Output can exceed the 5.0 GT/s Data Rate RMS jitter limit

Now according to our measurements and thoughts we are assuming, that there is an internal pulldown resistor that is responsible for our problem.

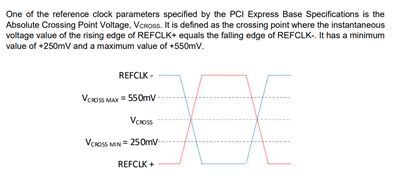

The voltage level is too low, not high enough according to the PCIe Standard (Voltage Cross).

Voltage Cross for PCIe Clock Signal:

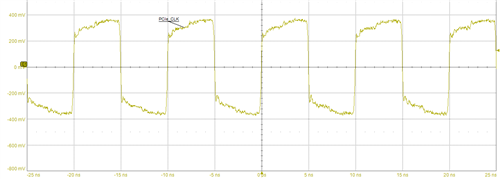

Here the signals that we are measuring, we see that we end up with a cross voltage of 200mV:

.

Is there any internal resistor, that can have influence at the CPU port W17 SERDES0_REFCLK0P and W18 SERDES0_REFCLK0P ?

Can you confirm that there is an internal termination resistor, if so if it is possible to turn it off and what register write we have to do to turn it off?