Tool/software:

Hi,

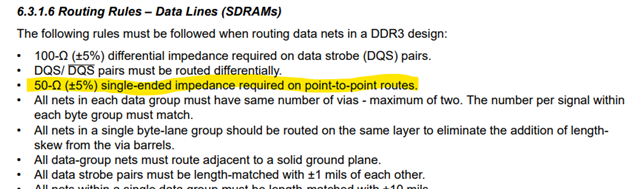

According to "DDR3 Design Requirements for Keystone Devices" (sprabi1d.pdf), 50ohm +/-5% impedance is required for single-ended impedance.

My customer is asking it is OK to relax the value to 50ohm +/-10%.

What is the reason to require +/-5%?

Thanks and regards,

Koichiro Tashiro