Part Number: J784S4XEVM

Tool/software:

Hi,

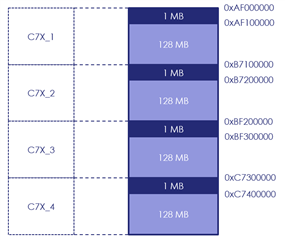

I am currently working with the custom memory layout in the Linux device tree :

While using rpmsg_char_simple tool on A72 Linux and the ipc_echo_test example on C7X DSP with the attached memory layout.

We faced the following error : "_rpmsg_char_find_ctrldev: could not find the matching rpmsg_ctrl device for virtio1.rpmsg_chrdev.-1.14" for DSP3 and DSP4.

DSP1 and DSP2 IPCs are working correctly.

All DSPs are attached. I see this with the command : "cat /sys/class/remoteproc/remoteproc*/state"

Is there a problem with my custom memory layout ?

Regards,

Bruce