Part Number: AM6421

Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

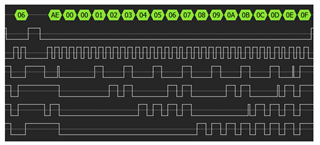

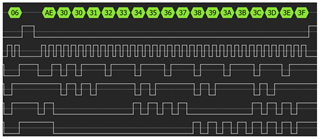

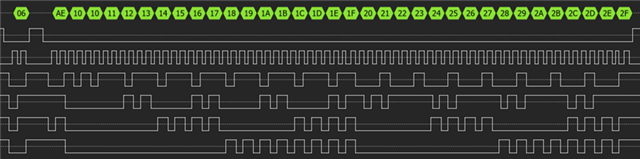

In direct mode, the clock is 10 M.

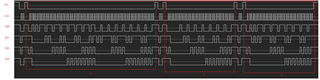

By calling the interface as shown in the figure above, the waveform is as follows.

A frame is split into three frames.

I want to know if this phenomenon is correct?