Tool/software:

I installed processor-sdk-rtos-j784s4-evm-10_00_00_05, and try to build on Ubuntu Linux environment, but it failed

cd ~/ti/ti-processor-sdk-rtos-j784s4-evm-10_00_00_05/mcusw/build

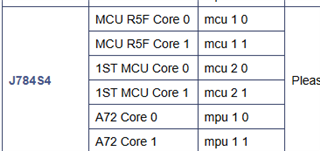

~/ti/ti-processor-sdk-rtos-j784s4-evm-10_00_00_05/mcusw/build$ make -s all BOARD=j784S4_evm SOC=j784S4 CORE=mcu2_1

~/ti/ti-processor-sdk-rtos-j784s4-evm-10_00_00_05/pdk_j784s4_10_00_00_27/packages/ti/boot/sbl/sbl_component.mk:184: *** first argument to 'word' function must be greater than 0. Stop.

If I need build app for main domain R5F, which CORE should be specified ? CORE=main1_0 ? I don't find any example for CORE=r5f1_0 or CORE=main2_1, even on PDK side.

Could you provide the examples( and build instruction) that can be built for main domain ?

Thanks