Hello,

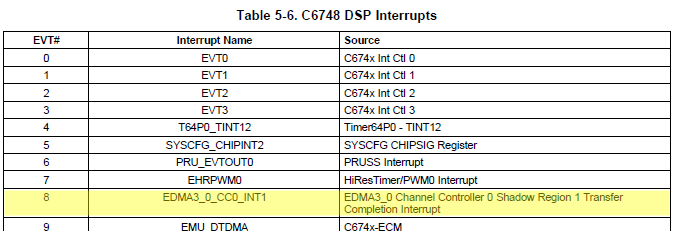

I'm trying to setup EDMA to the McASP, and am still not clear on DMAQNUM and DRAE.

For DRAE, some example code I have uses region 1 for EDMA, which I've designed in as below, for the McASP transmit and receive:

for Tx, CSL_FINST( EDMA3->DRA[ 1 ].DRAE, EDMA3CC_DRAE_E1, ENABLE );

for Rx, CSL_FINST( EDMA3->DRA[ 1 ].DRAE, EDMA3CC_DRAE_E0, ENABLE );

Does that seem right, and why region 1, instead of the DMA Region Access Enable Registers for region 0, 2 or 3?

For DMAQNUM, once again example code showed DMAQNUM0 being used, and Q0 for it. But why not DMAQNUM 0, 2 or 3? Also, for the DMAQNUM, can I use Q0 for the transmit to McASP and Q1 for receiving from it, like below?

for Tx, CSL_FINST( EDMA3->DMAQNUM[ 1 ], EDMA3CC_DMAQNUM_E1, Q0 );

for Rx, CSL_FINST( EDMA3->DMAQNUM[ 1 ], EDMA3CC_DMAQNUM_E0, Q1 );

Please advise,

Robert