Tool/software:

Dear supporter,

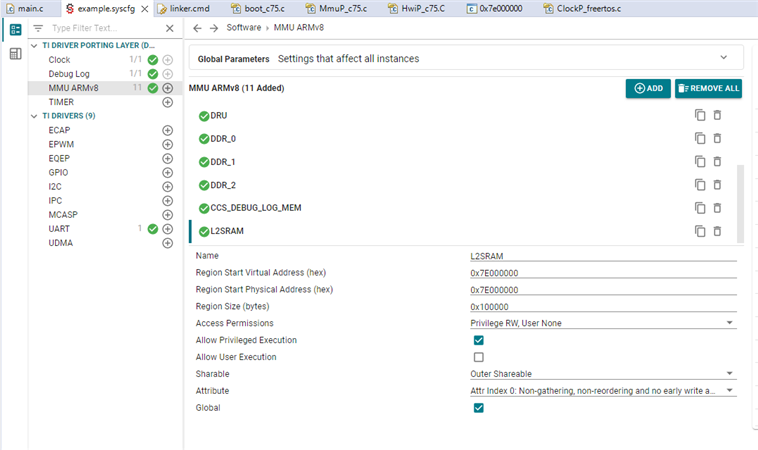

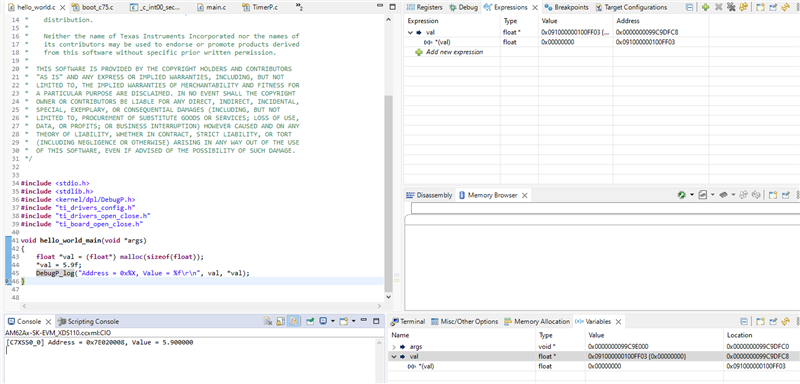

I'm trying to run C7x hello world Freertos example on MCU SDK 10 using L2SRAM. The default linker routes all section to DDR, I need the stack and heap route to L2SRAM. But I can only point the .sysmem to SRAM. Whenever I point the .stack to SRAM, the debugger cannot jump to main function. Could you please help me change the linker to make hello world Freertos project run on SRAM?

Thank you very much!