Other Parts Discussed in Thread: SK-AM62-LP

Tool/software:

Hi, Dear Expert

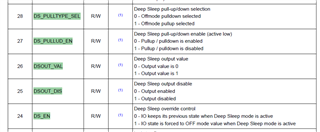

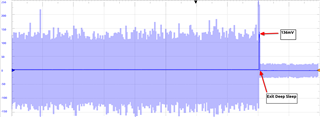

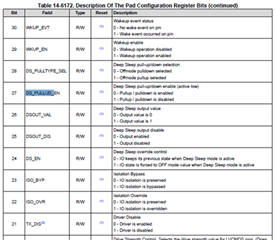

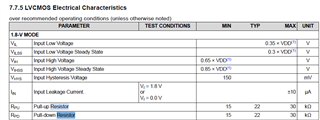

As title description, customer wants to keep "last I/O status" after SoC swap into "deep sleep" or "partial I/O" mode.

for example, gpio0_49 = low is in "normal active mode", and then we hope gpio0_49 "keep low" when SoC swap into "deep sleep" or "partial I/O" mode.

Is it possible?

or Could we set each GPIO status when SOC (AM62) swap into "deep sleep" or "partial I/O" mode?

Thank you very much

Gibbs