Tool/software:

Hello Expert,

I have built SDK9.2 version software for Ethfw and Vision apps for MCU2_0 (server) MCU2_1 (client),

case 1 : binaries from Ethfw build for MCU2_0 and MCU2_1 are working fine and able to communication through IPC and Ethernet TX and Rx are working on both Client and Server.

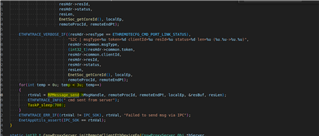

Case2 : MCU2_0 binary is from vision apps (platform build ) and MCU2_1 is from Ethfw (app_remoteconfig_client) here IPC handshake is not working to create virtual instances, could you please let us know what could be the issue? are these compatible with memory layouts?

Thanks and Regards,

Satya.