Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi

We are using AM6421 with SDK

1) Processor SDK Linux for AM64x Version: 09.02.01.10

2) mcu_plus_sdk_am64x_09_02_00_50

We have configured CPSW port in RMII mode, below is our interface details

Can you suggest us if these settings can be used.

We are unable to configure the MDIO signals in sysconfig.

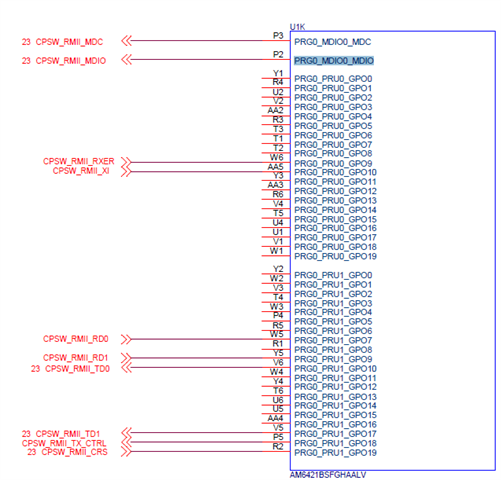

CPSW_RMII_MDC - PRG0_MDIO0_MDC

CPSW_RMII_MDIO- PRG0_MDIO0_MDIO.

We are using the DP83822 phy.