Part Number: TDA4AL-Q1

Tool/software:

Dear expert,

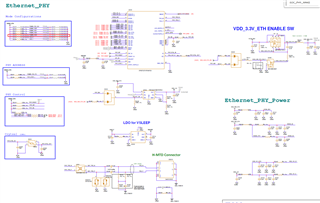

we can't get PHY IC address 0 even we check the address is correct. strap mode we select 1 and RX_CTRL Strap mode also select 1. and after measure, we the HW signal also correct.

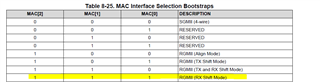

Could you help to confirm if MAC interface selection will impact PHY address reading? current our board default MAC selection is 111. Seem that is RGMII (RX SHift mode) , is it suit for TDA4AL SOC setting?

U-Boot MCU SPL 2024.04-ti-g818c76aed67f (Aug 01 2024 - 19:19:47 +0000) SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') EEPROM not available at 0x50, trying to read at 0x51 Reading on-board EEPROM at 0x51 failed -121 SPL initial stack usage: 13456 bytes Trying to boot from MMC1 Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Loading Environment from nowhere... OK init_env from device 17 not supported! Starting ATF on ARM64 core... NOTICE: BL31: v2.10.0(release):v2.10.0-367-g00f1ec6b87-dirty NOTICE: BL31: Built : 16:09:05, Feb 9 2024 I/TC: I/TC: OP-TEE version: 4.2.0-dev (gcc version 13.3.0 (GCC)) #1 Fri Apr 12 09:51:21 UTC 2024 aarch64 I/TC: WARNING: This OP-TEE configuration might be insecure! I/TC: WARNING: Please check https://optee.readthedocs.io/en/latest/architecture/porting_guidelines.html I/TC: Primary CPU initializing I/TC: GIC redistributor base address not provided I/TC: Assuming default GIC group status and modifier I/TC: SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') I/TC: HUK Initialized I/TC: Activated SA2UL device I/TC: Fixing SA2UL firewall owner for GP device I/TC: Enabled firewalls for SA2UL TRNG device I/TC: SA2UL TRNG initialized I/TC: SA2UL Drivers initialized I/TC: Primary CPU switching to normal world boot U-Boot MCU SPL 2024.04-ti-g818c76aed67f (Aug 01 2024 - 19:19:47 +0000) SYSFW ABI: 4.0 (firmware rev 0x000a '10.0.8--v10.00.08 (Fiery Fox)') i2c_omap i2c@42120000: pinctrl_select_state_full: uclass_get_device_by_phandle_id: err=-19 EEPROM not available at 0x50, trying to read at 0x51 Reading on-board EEPROM at 0x51 failed -121 Trying to boot from MMC1 Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted Warning: Detected image signing certificate on GP device. Skipping certificate to prevent boot failure. This will fail if the image was also encrypted U-Boot 2024.04-ti-g818c76aed67f (Aug 01 2024 - 19:19:47 +0000) SoC: J721S2 SR1.0 GP Model: Texas Instruments J721S2 EVM i2c_omap i2c@42120000: pinctrl_select_state_full: uclass_get_device_by_phandle_id: err=-19 EEPROM not available at 0x50, trying to read at 0x51 Reading on-board EEPROM at 0x51 failed -121 Board: J721S2X-PM1-SOM rev E1 DRAM: 2 GiB (effective 8 GiB) Core: 114 devices, 31 uclasses, devicetree: separate Flash: 0 Bytes MMC: mmc@4f80000: 0, mmc@4fb0000: 1 Loading Environment from FAT... i2c_write: error waiting for data ACK (status=0x116) pca953x gpio@22: Error reading output register Card did not respond to voltage select! : -110 mmc_init: -95, time 75 ** Bad device specification mmc 1 ** In: serial@2880000 Out: serial@2880000 Err: serial@2880000 am65_cpsw_nuss ethernet@46000000: K3 CPSW: nuss_ver: 0x6BA02102 cpsw_ver: 0x6BA82102 ale_ver: 0x00293904 Ports:1 EEPROM not available at 0x50, trying to read at 0x51 Reading on-board EEPROM at 0x51 failed -121 Net: Could not get PHY for mdio@f00: addr 0 am65_cpsw_nuss_port ethernet@46000000port@1: phy_connect() failed No ethernet found. Hit any key to stop autoboot: 0 => mdio list mdio@f00: