Other Parts Discussed in Thread: SYSCONFIG, SK-AM62-LP, UNIFLASH

Tool/software:

Hi!

When I used an older version of the MCU+ SDK for AM62x, such as 10.00.00.14, I was unable to boot the image from the SBL NULL using NOR flash. The bootloader complained, "Failed to authenticate Image." However, after upgrading the SDK to the latest version (10.01.00.33), I managed to boot the image and load the M4 app from CCS. I noticed that it still produces a warning saying, "Failed to authenticate and copy on the go, reading the image to DDR."

When I changed the OSPI's Input Clock Divider to a value larger than 2, the SBL NULL still refused to boot, displaying the same "Failed to authenticate Image" error in addition to the warning message mentioned above. The same issue occurs when setting the Input Clock Frequency and Divider to combinations below 166MHz / 2, such as 20MHz / 2, 166MHz / 4, 166MHz / 32, etc. Despite this, I verified that NOR flash read/write operations work normally for all these settings by adding read/write/erase test code to the SBL NULL before executing the actual bootloader operations.

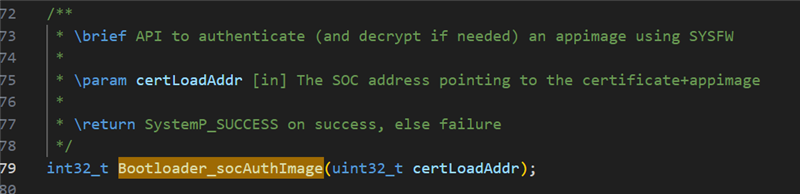

Upon debugging the SBL NULL code, I found that no TISCI_MSG_FLAG_ACK was returned when making TISCI_MSG_PROC_AUTH_BOOT calls with Sciclient_service after the image was copied to DDR while using a lower OSPI Input Clock speed. However, TISCI_MSG_FLAG_ACK is set when using the 166MHz / 2 setting. Could this issue be related to SYSFW?

Please help me with successfully authenticating and loading the image when using a lower clock speed on NOR flash. Thank you!

BR,

Zijian XU.