Other Parts Discussed in Thread: TDA4VL

Tool/software:

Hi expert,

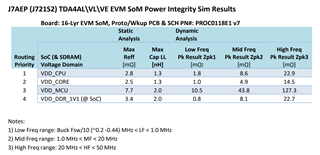

Our customer is doing TDA4VL PI simulation. They would like to know if the below result consider the impact of VRM? How to set the VRM parameter? Thank you

Best Regards,

Xingyu Zhu

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

The VRM (voltage regulator) is not part of the PCB PDN PI simulation. The VRM & power inductor should be "removed" from sim model and 2x simulation ports should be attached as follows:

1.Across the SoC power supply input pins connected to the power rail being evaluated to VSS/Gnd.

2. Across the VRM's bulk capacitors connected to the power rail being evaluated to VSS/Gnd.

During PI sim, the "VRM Bulk Cap port" will be shorted as the simulation "looks back into the PDN network" consisting of the PCB routing & PDN decoupling capacitors (both bulk & high-freq caps attached to the power rail under simulation) from the SoC input supply sim port. This enables the PI sim to evaluate just the PCB layout design and the PDN decoupling scheme impedance vs freq response.