Tool/software:

Tool/software:

Hi

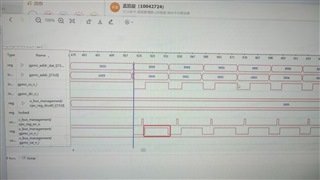

Customer now are testing AM243 customer board with GPMC accessing FPGA.

The mode is configured as single access with a data width of 16 bits, non-multiplexed.

From the timing point of view, there is a large gap between the completion of each read and write and the start of the next packet of data.

Now they tried modified this Bit8 and Bit11 but the gap only increase, can not decrease. With 0, Gap is 200ns, with larger cycle, gap will be larger. So how to eliminate this gap? Thanks for your help.

Regards

Zekun