Tool/software:

Hello, Please use this thread as a continuation of the email and TI-Internal e2e forum discussion.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

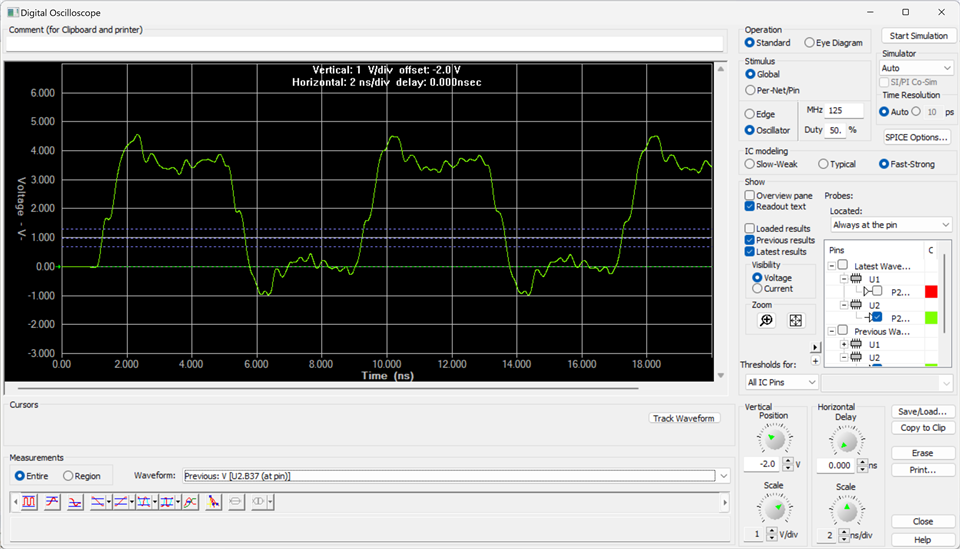

As discussed previously, I see meaningful ripples when using the TDA as my RGMII Rx.

Those ripples are PVT and rise time depended.

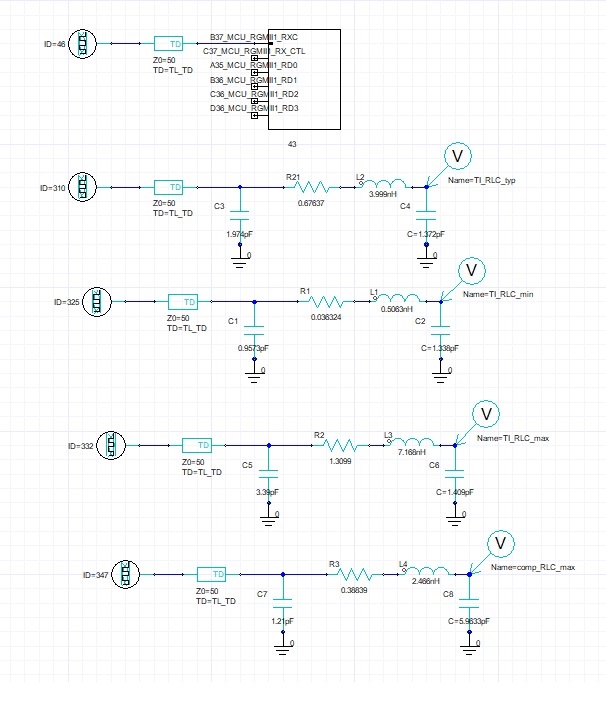

Please see below plots with:

1. TDA at PVT-max (DS-LVCMOS0_fast)

2. Tx is an ideal 50 ohm driver, Tr-0.4ns, clk pattern 4ns UI.

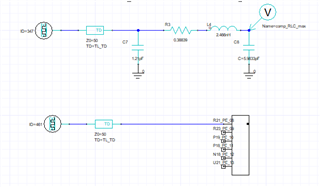

3. For debug - used same setup with RLC circuit from TDA ibis file and compared against 3rd party RGMII Rx RLC.

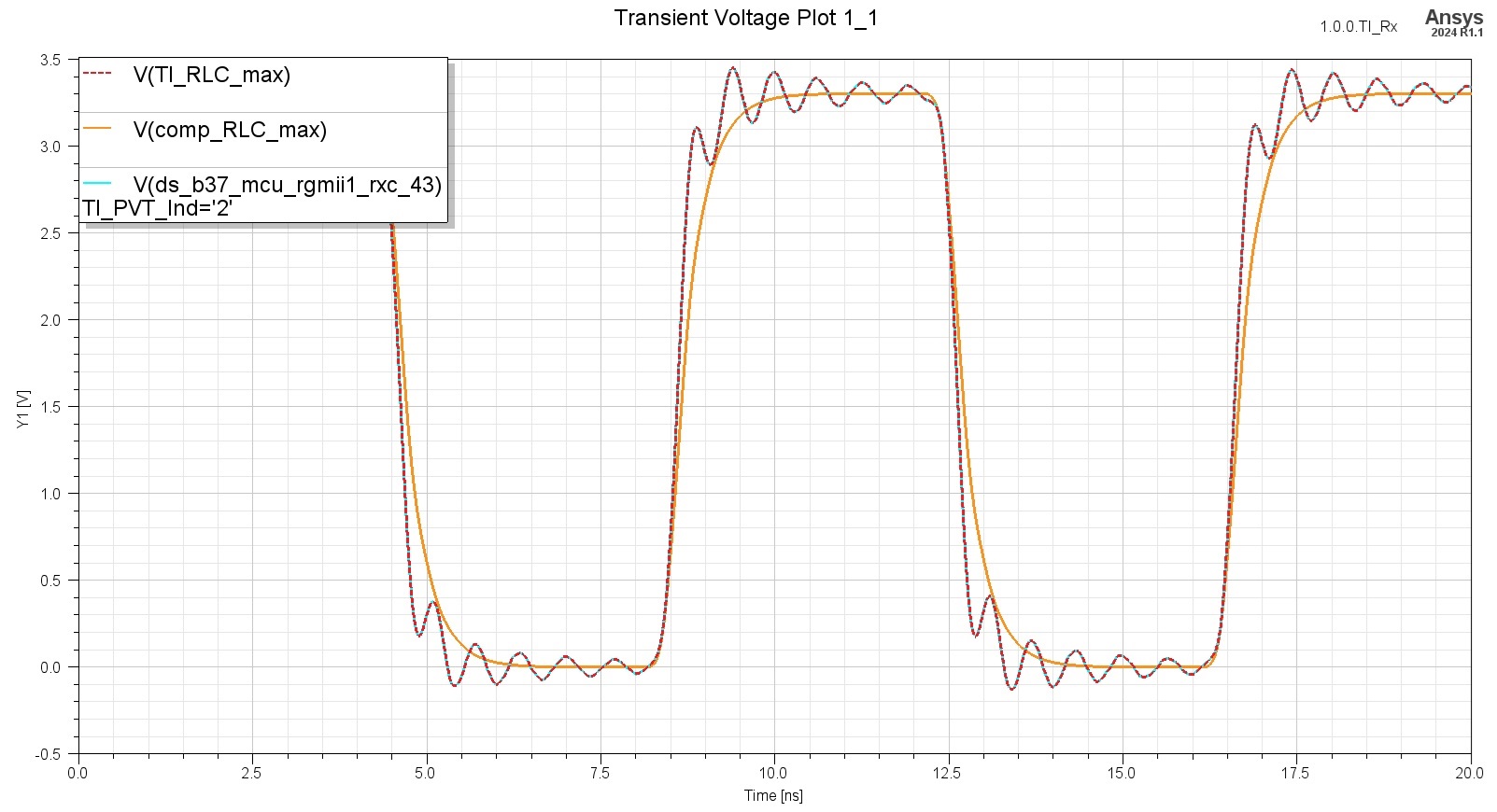

Please see below plots for PVT max (where ripples are strongest):

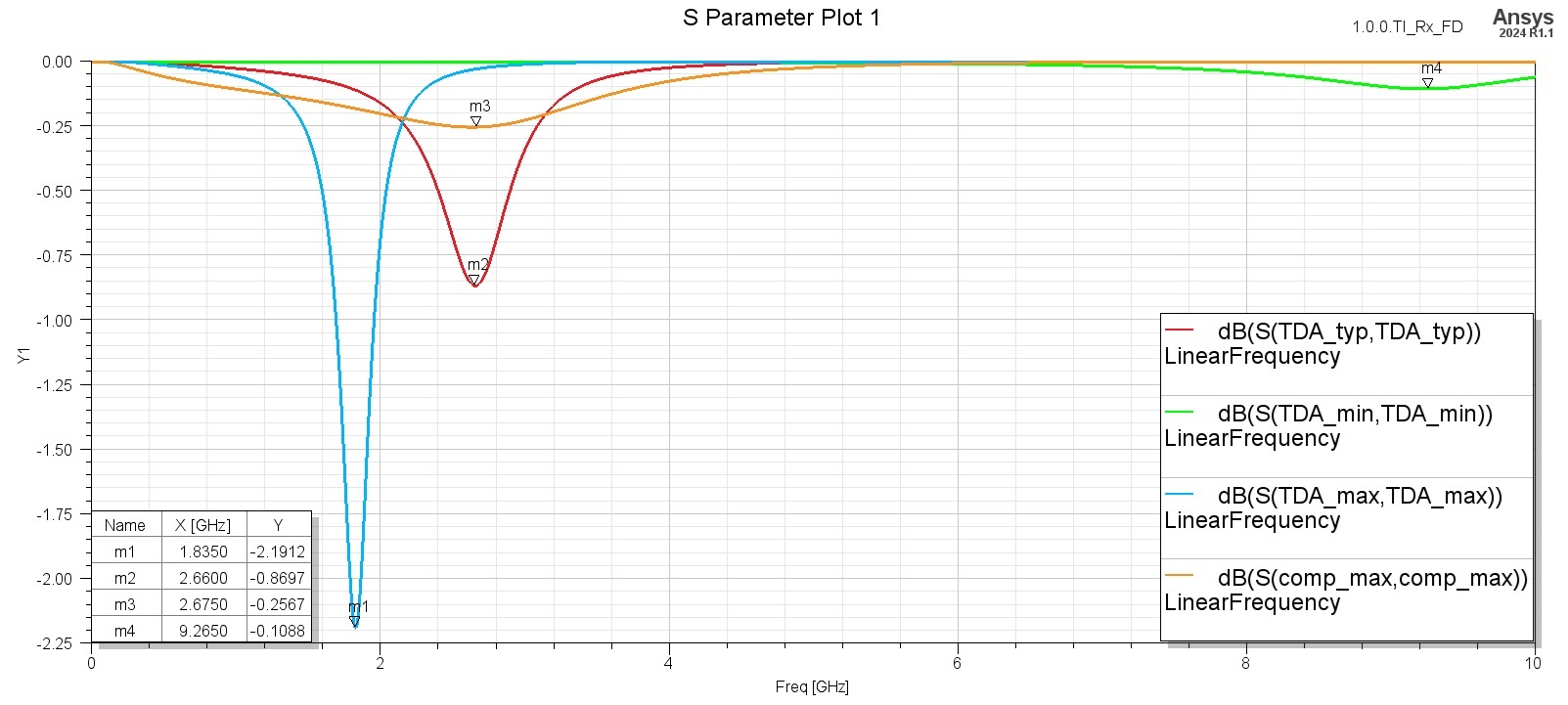

I suspect the root cause is in frequency domain of RLC - look at return loss plots below:

Waiting for reply,

Yoel

Hi Yoel,

Could you please try this IBIS model with updated LVCMOS and SDIO buffers?

Regards,

Mark

Hi Yoel,

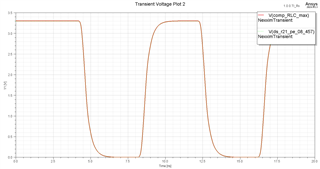

Thank you for the plot of both the 0p1 and 0p2 model— the updated LVCMOS model looks better.

To rule out any IBIS issues, could you please replace our RLC values with the competitor's RLC values and see if the issue still exists?

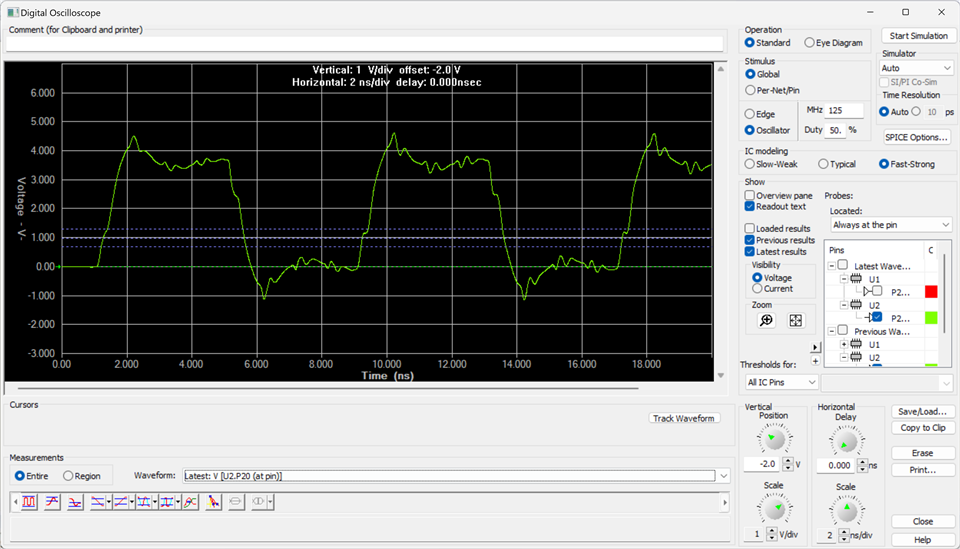

Using HyperLynx, I ran a sim using the 3rd-party TX to the same 3rd-party RX. The results look similar to the 3rd-party TX to TI RX. We suggest working with 3rd party to understand options to improve signal integrity with their TX.

Parameters:

3rd-party TX to 3rd-party RX

3rd-party TX to TI RX

Regards,

Mark

Hi Mark,

To clarify, in all recent plots I sent I used an ideal 50 ohm driver with 0.4ns rise time, not 3rd party Tx.

Below are voltage plots at PVT max of 3rd party, RLC Vs. ibis to validate there is no ibis modelling issue.

Regarding the plots you sent, not sure exactly what you used, but looks like you have almost 4.5V peak and -1V min. Are you sure of your setup? not reasonable for RGMII, as far as I know...

To summarize, I have an ideal 50 ohm driver and I test 2 different receivers, using ibis and RLC.

With TI I get strong ripples at typ and max PVT (ibis and RLC) , with 3rd party I don't.

I can see TI RLC circuit has a significant resonance at BW of rise time which explains the ripples.

Hi Yoel,

I talked with our simulation expert and he recommended to use RLC values from the [Package Model] section and not the [Package] section. The [Package Model] section has RLC values for a given pin of interest whereas the [Package] section has RLC values for a typical pin.

For some convenience, here are the RLC values for pin B37 on our device from the [Package Model] section:

Regards,

Mark