Tool/software:

Hello experts,

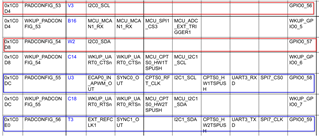

For my custom boards, we use V3,W2,U3,T3 as normal gpio to enable or disable somethings. But however, the pinmux registers of balls V3 and W2 are a litte different from the other two.

It seems that, V3 and W2 have only two mux modes, and the default usage is to I2C, I want to use it as normal gpio and can pull it up and down, so, the mux value should be 7. However, V3 and W2 have no PULLTYPESEL configure bit of there control registers:

So, we configure the pinmux controls use macro J721E_IOPAD(offset, PIN_OUTPUT_PULLUP, 7) and the control the gpio sysfs to control the 4 pins, will make the control registers value to 0x20007 for U3 and T3, 7 for V3 and W2. And the control from sysfs works for U3 and T3, but does not work for V3 either W2.

So, I want to know what's the right configure value for CTRLMMR_PADCONFIG53 and CTRLMMR_PADCONFIG54 to make pad V3 and W2 working well as other normal GPIOs?

Thanks