Hi,

I would like to ask a question on OMAP L138 power.

Standby and Deepsleep

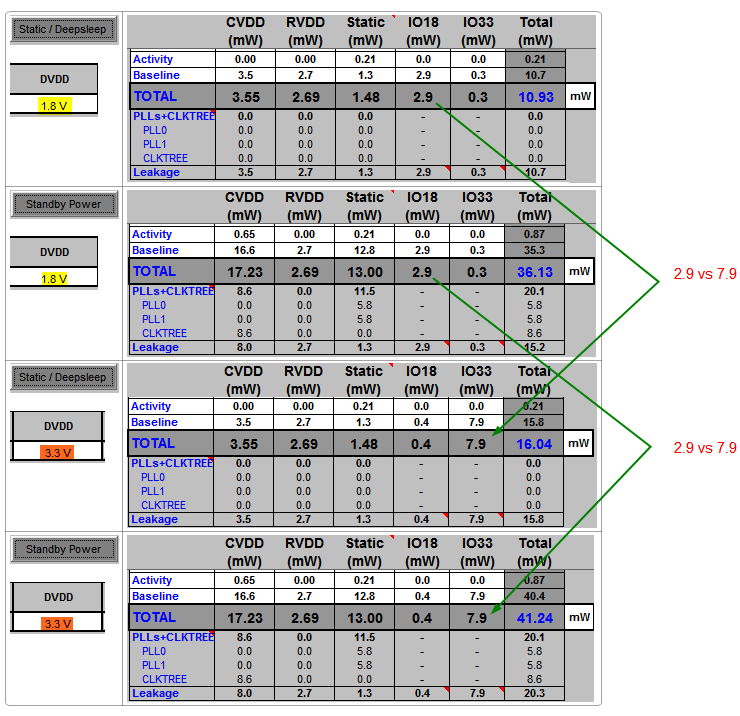

I used power consumption spreadsheet to calculate deepsleep and standby mode power, and found there is a 5mW (2.9 vs 7.9) difference due to IO18 and IO33 difference:

Why do they still consume power at rest?

Due to pin-muxing, there are probably no less than 150 pins on L138 that could function as GPIO. The crucial question is: when these pins are not used and are corrected connected to avoid any avoidable leakage, do they still consume power?

The spreadsheet result clearly suggests yes, but why?

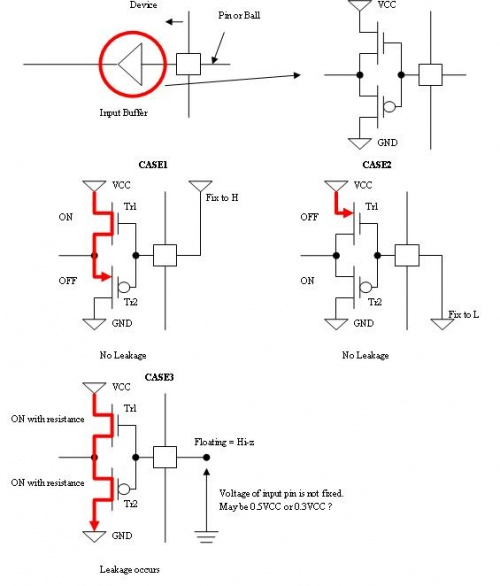

According to http://processors.wiki.ti.com/index.php/Optimizing_IO_Power_Consumption, GPIO leakage happens only when there is a floating input pin. Therefore, when all GPIO pins are either set as output, or as input with non-floating voltage, then is there still any leakage here?

When an I/O pin is not used, does it still consume any power? There can be two cases for "not used":

1. Set as output, but unconnected or connected to the same voltage as its output, thus not driving anything.

2. Set as input, and with fixed voltage.

I guess it might still consume some power, because also according to http://processors.wiki.ti.com/index.php/Optimizing_IO_Power_Consumption#Internal_pull-up.2Fdown_case:

TI' standard pull-up/down cell is current source, not actual resistance. This current source fixes voltage level when pin is floating. When pin with pull-up cell is tied to H, there is no current flow. But when this pin is fixed to L, device leakage occurs. See Figure - 3 CASE3. Also when the pin with pull-down cell is fixed to H, system leakage occurs. This is not device leakage.

I am quite ignorant on the physics of the puling-up/down current source here; but as long as it is an electronic component, it must consume some power. Excluding "system leakage" above which is due to incorrect connection practice, for (1) and (2) of "not used" case above: is there any leaking current and henceforth power consumption? Why?

Zheng