Tool/software:

Hello TI experts:

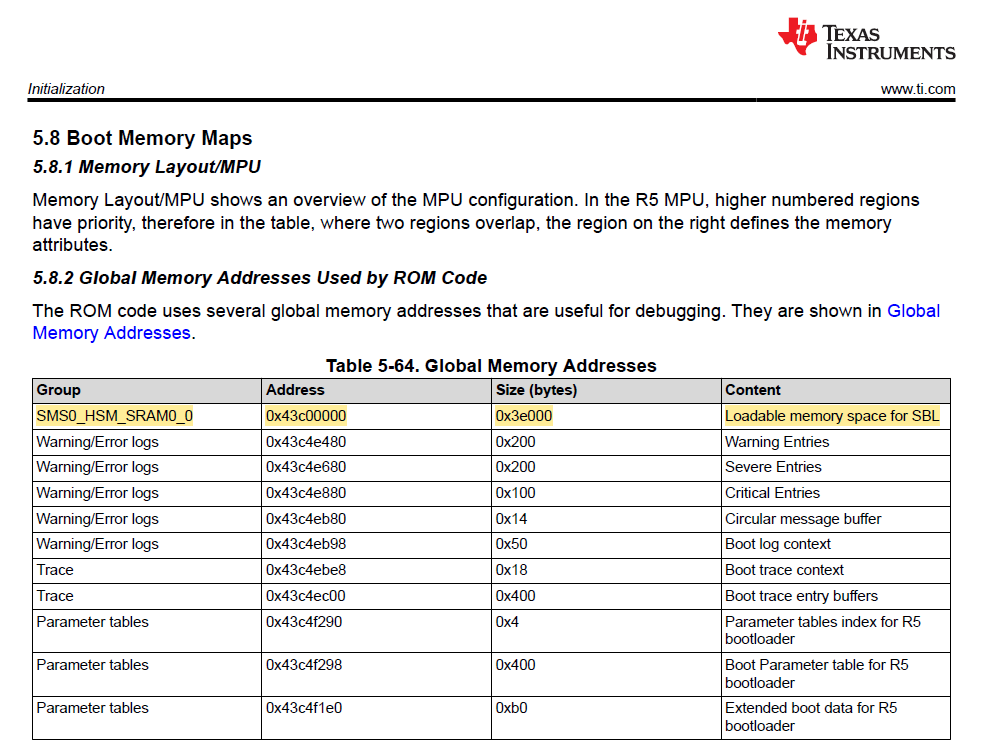

I’m seeing that the start-address of the U-Boot SPL R5 code is 0x43c00000. That’s confirmed by the corresponding device tree node, the u-boot-spl.lds file, and some debug code I have added.

In theory, some type of RAM memory needs to be present in that address range of the SoC since the U-Boot code needs to be loaded by the ROM and DM-R5. However, I can find no corresponding entry in the memory map of the AM62P. The closest entry I find is called MSRAM_64K0_RAM, but it’s located at 0x43C40000 in the MAIN memory map:

The WKUP_R5FSS0 and MCU_R5FSS0 memory maps don’t show anything useful either and the “Region Address Translation” (RAT) function (seemingly) also cannot (or should not?) be used to remap memory in that area (from page 631 of the AM26P TRM):

Obvious question:

What's the "magic" here?