1464.VideoPhyTest_evmc6670.rar

Please find attached

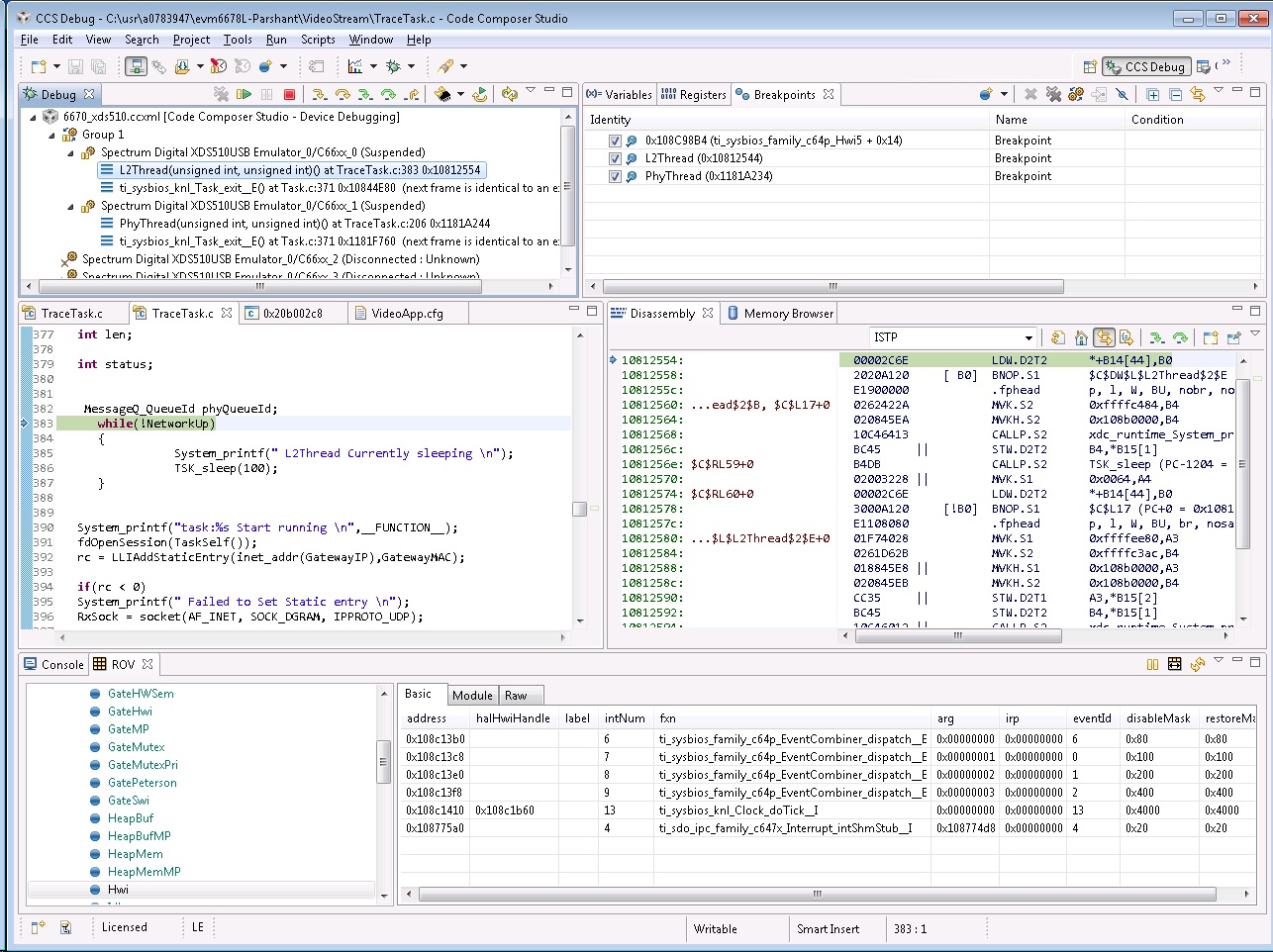

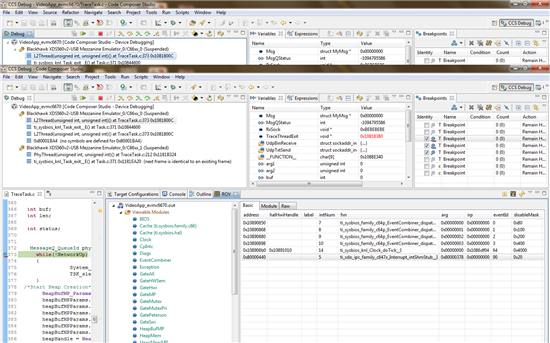

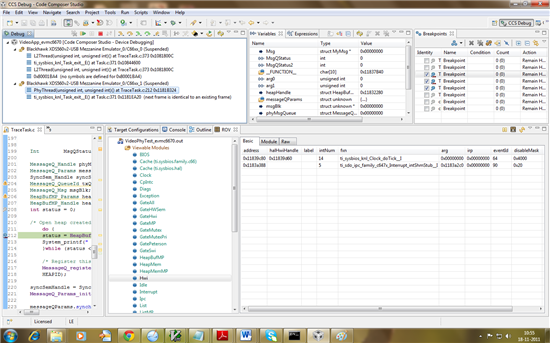

1. VideoStream.rar: Contains core 0 code. This code defines two task TraceThread and L2thread.

--L2Thread: Recv packet from socket and write on Core 1 messageQ.

--TraceThread: Reads data on the message queue and send it on socket.

2. VideoPhyTest_evmc6670 : Core 1 code. This code will create a phythread on core 1.

-- Core 1 reads data from its message queue and dump data back to TraceThread(Core 0) message queue.

All queues use the same heap define in Shared memory region(DDR3).

Issue:

--L2thread when trying to open messageQ of Phythread

}

System_printf(" Bind Succesfully\n");

do

{

System_printf("L2Thread going to sleep\n");

(hangs)-->status = MessageQ_open(SOCKINMSGQ, &phyQueueId);

System_printf("status:%d\n",status);

TSK_sleep(500);

System_printf("L2Thread is awake\n");

}while(status < 0);

System_printf("Phy Message Queue open Successfully\n");

---Phythread also hangs when open messageQ of TraceThread

while (MessageQ_open(SOCKOUTMSGQ, &txQueueId)< 0)

{

System_printf("PhyThread going to sleep");

TSK_sleep(500);

System_printf("PhyThread is awake");

}

Regards,

Parshant