Other Parts Discussed in Thread: SK-AM62-LP, AM623, AM625

Tool/software:

Hello,

I am designing a board to evaluate the many features of the AM6442. I am using the EVM and StarterKit as references for my design, but I am encountering difficulties due to the large number of ferrites in the power circuit of the AM6442.

I referred to the following URL, which suggests optimizing the number of ferrites by referring to the SK-AM62-LP:

[FAQ] AM625 / AM623 Custom board hardware design – Ferrite (power supply filter) recommendations for SoC supply rails

e2e.ti.com/.../faq-am625-am623-custom-board-hardware-design-ferrite-power-supply-filter-recommendations-for-soc-supply-rails

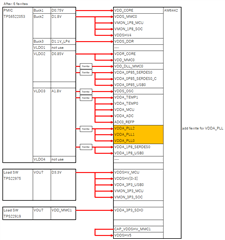

After reviewing the above URL, I managed to reduce the number of ferrites from 10 to 6. Below are the details of the changes made. Could you please advise if it is possible to reduce the number further?

The number of ferrites for VDDS_OSC has increased. Are these necessary?

The ferrite for VDDAR_0P85_USB0 has been removed. Is it unnecessary?

The SK-AM62-LP does not have ferrites for VDDA_ADC, VDD_DLL_MMC0, and VDDAR_0P85_SERDES0. Can these ferrites be removed?

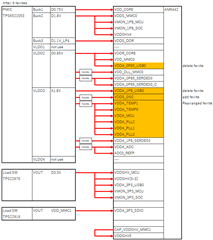

Before: 10 ferrites

VDDA_CORE -> Ferrite -> VDDAR_0P85_SERDES0 -> [AM64] VDDA_0P85_SERDES0, VDDA_0P85_SERDES0_C

VDDA_CORE -> Ferrite -> VDDAR_0P85_USB0 ----> [AM64] VDDA_0P85_USB0

VDDA_CORE -> Ferrite -> VDD_DLL_MMC0 -------> [AM64] VDD_DLL_MMC0

VDDA_1V8 --> Ferrite -> VDDA_1V8_SERDES ----> [AM64] VDDA_1P8_SERDES0

VDDA_1V8 --> Ferrite -> VDDA_ADC -----------> [AM64] VDDA_ADC, ADC0_REFP

VDDA_1V8 --> Ferrite -> VDDA_1V8_USB0 ------> [AM64] VDDA_1P8_USB0

VDDA_1V8 -----------------------------------> [AM64] VDDS_OSC

VDDA_1V8 -----------------------------------> [AM64] VDDA_TEMP0

VDDA_1V8 -----------------------------------> [AM64] VDDA_TEMP1

VDDA_1V8 --> Ferrite -> VDDA_PLL0 ----------> [AM64] VDDA_PLL0

VDDA_1V8 --> Ferrite -> VDDA_PLL1 ----------> [AM64] VDDA_PLL1

VDDA_1V8 --> Ferrite -> VDDA_PLL2 ----------> [AM64] VDDA_PLL2

VDDA_1V8 --> Ferrite -> VDDA_1V8_MCU -------> [AM64] VDDA_MCU

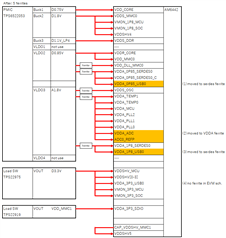

After: 6 ferrites

VDDA_CORE -> Ferrite -> VDDAR_0P85_SERDES0 -> [AM64] VDDA_0P85_SERDES0, VDDA_0P85_SERDES0_C

VDDA_CORE ----------------------------------> [AM64] VDDA_0P85_USB0

VDDA_CORE -> Ferrite -> VDD_DLL_MMC0 -------> [AM64] VDD_DLL_MMC0

VDDA_1V8 --> Ferrite -> VDDA_1V8_SERDES ----> [AM64] VDDA_1P8_SERDES0

VDDA_1V8 --> Ferrite -> VDDA_ADC -----------> [AM64] VDDA_ADC, ADC0_REFP

VDDA_1V8 -----------------------------------> [AM64] VDDA_1P8_USB0

VDDA_1V8 --> Ferrite -> VDDA_1V8_FB_OSC ----> [AM64] VDDS_OSC

VDDA_1V8 --> Ferrite -> VDDA_1V8_FB1 -------> [AM64] VDDA_TEMP[0-1], VDDA_PLL[0-2], VDDA_MCU