Tool/software:

I use TDA4VM, SDK 10.0.08, 2.5Gbps PHY chip.

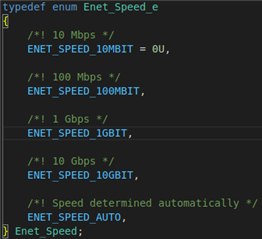

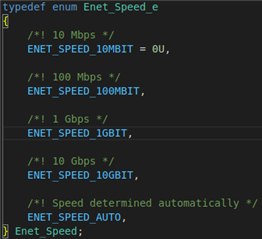

The ETHFW is used. There is no definition of 2.5Gbps in the code here, how to set Port1 and Port2 of CPSW9G to 2.5Gbps mode?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

I use TDA4VM, SDK 10.0.08, 2.5Gbps PHY chip.

The ETHFW is used. There is no definition of 2.5Gbps in the code here, how to set Port1 and Port2 of CPSW9G to 2.5Gbps mode?

Hi,

The ETHFW is used. There is no definition of 2.5Gbps in the code here, how to set Port1 and Port2 of CPSW9G to 2.5Gbps mode?

2.5Gbps is like extended SGMII which is 2.5 times of SGMII clock.

SerDes to be configured in XAUI interface with 156.25MHz clock and cpsw port has to configured in SGMII with 1Gbps speed.

Best Regards,

Sudheer

To use ETHFW CPSW9G, set Port1 and Port2 to 2.5Gbps SGMII.

Now with the following configuration, Port2 cannot link up peripherals (Port1 and peripherals are ignored here), where am I still having problems with the configuration?

ethfw/utils/board/src/j721e/board_j721e_evm.c

static EthFwBoard_MacPortCfg gEthFw_gesiMacPortCfg[] =

{

{ /* SGMII-2.5Gbps SerDes-0 LAN0 PHY */

.macPort = ENET_MAC_PORT_1,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_SERIAL },

.phyCfg =

{

.phyAddr = 0U,

.isStrapped = BFALSE,

.skipExtendedCfg = BFALSE,

.extendedCfg = &gEnetGesiBoard_dp83867PhyCfg,

.extendedCfgSize = sizeof(gEnetGesiBoard_dp83867PhyCfg),

},

.sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_WITH_PHY,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

},

{ /* SGMII-2.5Gbps SerDes-0 LAN1 Switch */

.macPort = ENET_MAC_PORT_2,

.mii = { ENET_MAC_LAYER_GMII, ENET_MAC_SUBLAYER_SERIAL },

.phyCfg =

{

.phyAddr = 1U,

.isStrapped = BFALSE,

.skipExtendedCfg = BFALSE,

.extendedCfg = NULL,

.extendedCfgSize = 0,

},

.sgmiiMode = ENET_MAC_SGMIIMODE_SGMII_FORCEDLINK,

.linkCfg = { ENET_SPEED_1GBIT, ENET_DUPLEX_FULL },

},

}

pdk_jacinto_10_00_00_27/packages/ti/board/src/j721e_evm/board_serdes_cfg.c

static Board_STATUS Board_CfgSgmii(void)

{

CSL_SerdesResult result;

CSL_SerdesLaneEnableStatus laneRetVal = CSL_SERDES_LANE_ENABLE_NO_ERR;

CSL_SerdesLaneEnableParams serdesLane0EnableParams = {0};

memset(&serdesLane0EnableParams, 0, sizeof(serdesLane0EnableParams));

/* SGMII Config */

serdesLane0EnableParams.serdesInstance = (CSL_SerdesInstance)SGMII_SERDES_INSTANCE;

serdesLane0EnableParams.baseAddr = CSL_SERDES_16G0_BASE;

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_156p25M;

serdesLane0EnableParams.refClkSrc = CSL_SERDES_REF_CLOCK_INT;

serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_3p125G;

serdesLane0EnableParams.numLanes = 0x2;

serdesLane0EnableParams.laneMask = 0x3;

serdesLane0EnableParams.SSC_mode = CSL_SERDES_NO_SSC;

serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_XAUI;

serdesLane0EnableParams.operatingMode = CSL_SERDES_FUNCTIONAL_MODE;

serdesLane0EnableParams.phyInstanceNum = SERDES_LANE_SELECT_CPSW;

serdesLane0EnableParams.pcieGenType = CSL_SERDES_PCIE_GEN3;

serdesLane0EnableParams.laneCtrlRate[0] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[0] = CSL_SERDES_LOOPBACK_DISABLED;

serdesLane0EnableParams.laneCtrlRate[1] = CSL_SERDES_LANE_FULL_RATE;

serdesLane0EnableParams.loopbackMode[1] = CSL_SERDES_LOOPBACK_DISABLED;

CSL_serdesPorReset(serdesLane0EnableParams.baseAddr);

/* Select the IP type, IP instance num, Serdes Lane Number */

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

0);

CSL_serdesIPSelect(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.phyType,

serdesLane0EnableParams.phyInstanceNum,

serdesLane0EnableParams.serdesInstance,

1);

result = CSL_serdesRefclkSel(CSL_CTRL_MMR0_CFG0_BASE,

serdesLane0EnableParams.baseAddr,

serdesLane0EnableParams.refClock,

serdesLane0EnableParams.refClkSrc,

serdesLane0EnableParams.serdesInstance,

serdesLane0EnableParams.phyType);

if (CSL_SERDES_NO_ERR != result)

{

return BOARD_FAIL;

}

/* Assert PHY reset and disable all lanes */

CSL_serdesDisablePllAndLanes(serdesLane0EnableParams.baseAddr, serdesLane0EnableParams.numLanes, serdesLane0EnableParams.laneMask);

/* Load the Serdes Config File */

result = CSL_serdesEthernetInit(&serdesLane0EnableParams);

/* Return error if input params are invalid */

if (CSL_SERDES_NO_ERR != result)

{

return BOARD_FAIL;

}

/* Common Lane Enable API for lane enable, pll enable etc */

laneRetVal = CSL_serdesLaneEnable(&serdesLane0EnableParams);

if (CSL_SERDES_LANE_ENABLE_NO_ERR != laneRetVal)

{

return BOARD_FAIL;

}

return BOARD_SOK;

}

If the Port2 SerDer is configured to the following parameters and the corresponding peripheral is also set to 1Gbps, it can work properly.

serdesLane0EnableParams.refClock = CSL_SERDES_REF_CLOCK_100M; serdesLane0EnableParams.linkRate = CSL_SERDES_LINK_RATE_1p25G; serdesLane0EnableParams.phyType = CSL_SERDES_PHY_TYPE_SGMII;

Hi,

If the Port2 SerDer is configured to the following parameters and the corresponding peripheral is also set to 1Gbps, it can work properly.

It seems PHY connected on Port-2 is set for SGMII with 1Gbps so, when you set the same CPSW SerDes side is working.

Please make sure the PHY/MAC connected to CPSW Port-2 is enabled in XAUI interface.

Best Regards,

Sudheer