Other Parts Discussed in Thread: TDA4VH, TDA4VM, TDA4VL

Tool/software:

I have downloaded the TDA4VH reference manual:

| User guide | J784S4 J742S2 Technical Reference Manual (Rev. D) |

However there seems to be some critical information missing from the PDF.

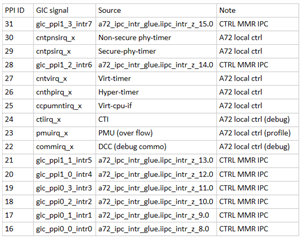

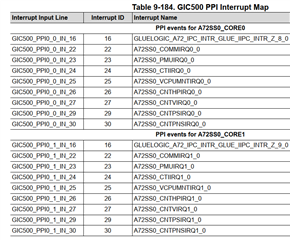

For example, I would like to see the PPI and SPI vector information for the GIC, but in the GIC section on page 804, section "9.2.1.2.2 GIC Interrupt Types" it just says:

The mapping of PPIs and SPIs can be found in section TBD .

As you can imagine, there is no "TBD" section.

Also, from what I can tell, the TDA4VH does not have an SMMU, but the documentation does say it supports PVU (peripheral virtualization unit). However on page 796, in the section 8.3.1.2 PVU Parameters, it says:

shows the PVU configuration parameters set during SoC design.

There is nothing else. The section is empty. On the other hand, in the TDA4VM manual, this section is populated.

Some related notes:

- With the TDA4VH documentation, some information is provided in the form of Excel spreadsheets. By contrast, the TDA4VM documentation is provided as PDFs only. Please note that Excel spreadsheets are much less convenient than PDFs.

- The interrupt input/output info provided in the "appedix" spreadsheet seems especially difficult to decipher.

- The PVU documentation does not show a real-world example of how to actually use the PVU. For example, if I software running on the A72 cores wanted to limit a particular DMA master so that it could only target specific RAM regions, what specific programming steps would be needed? Is there an application note somewhere that does a better job of explaining this?

-Bill