Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hello,team

sdk:ti-processor-sdk-linux-edgeai-am62axx-evm-09_02_00_05 & mcu_plus_sdk_am62ax_09_02_00_38

Chip model:

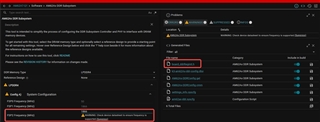

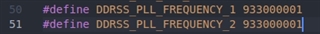

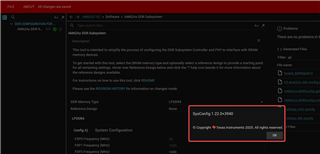

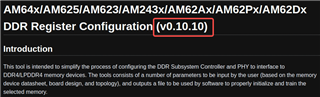

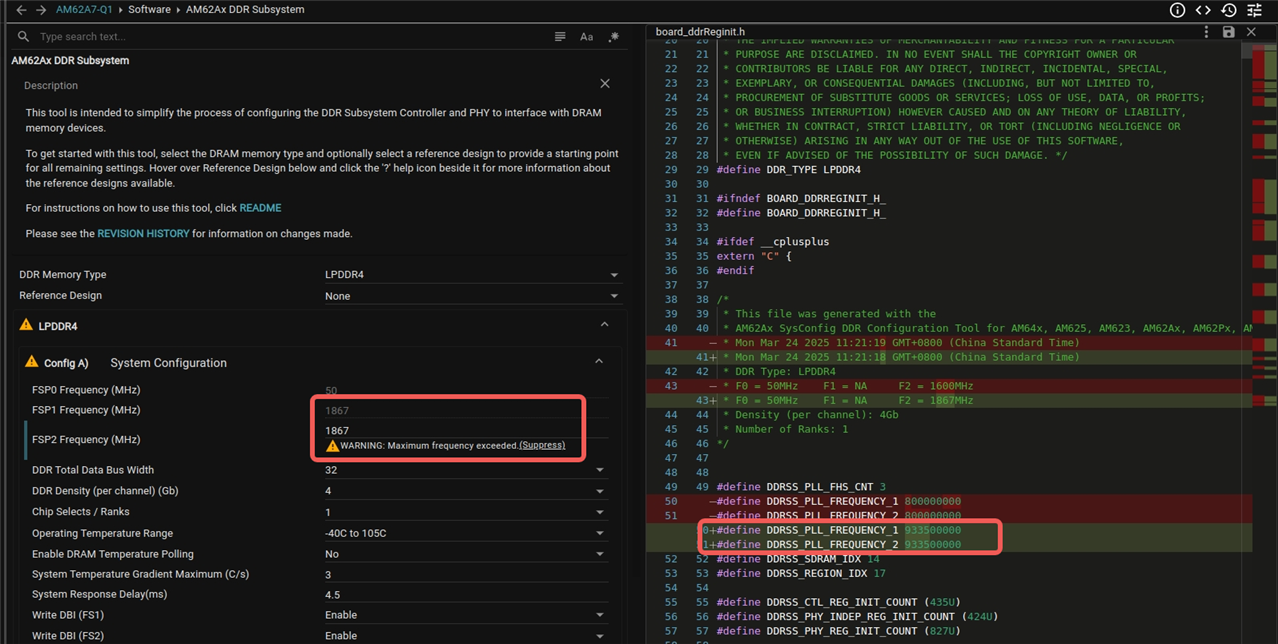

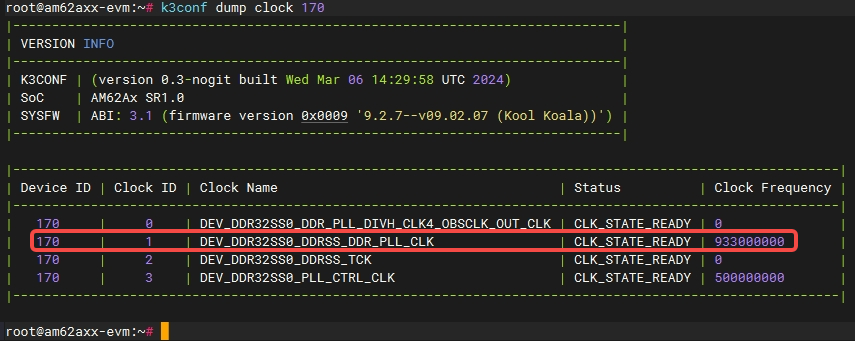

Due to the performance requirements of the project, we need to increase the DDR frequency, we are currently attempting to overclock to speed V using AM62A7 (speed U). The SPL startup program can start normally, and the DDR rate after startup is 3733MT/s, as shown in the following figure:

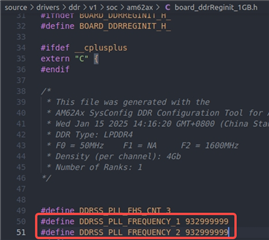

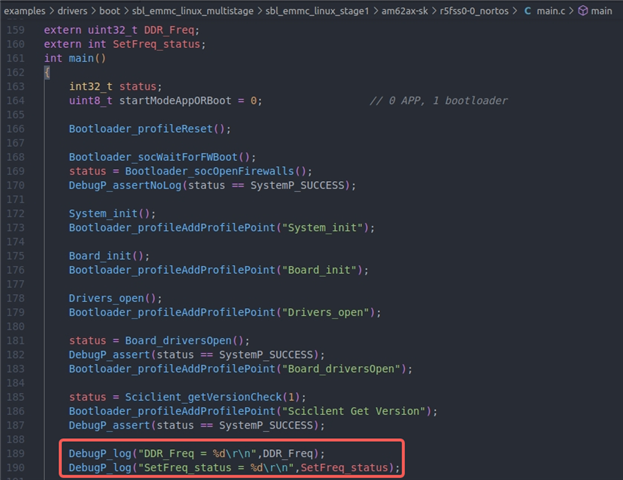

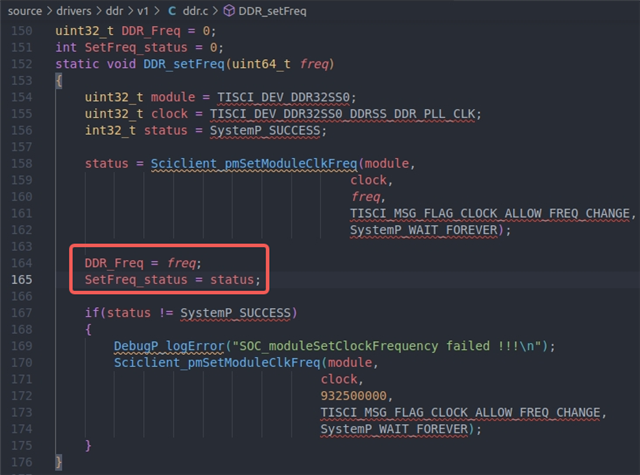

However, when we use SBL stage1 to start the program and set the rate to 3733MT/s, TISCI will return an error when setting the DDR clock frequency. The following figure is the source code of SBL stage1. In the section of setting DDR rate, I have added some debugging information, including frequency and return status values:

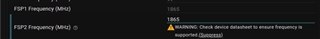

When the rate is set to 3733MT/s, an error value of -1 is returned and the startup fails:

![]()

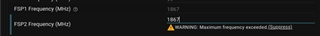

We tried other rates, such as changing it to 3730MT/s or 3734MT/s, and both were able to start successfully, with corresponding rates after startup,

![]()

![]()

![]()

![]()

May I ask if TISCI has imposed a restriction on 3733MT/s?