Tool/software:

Hi support,

I am evaluating the LCD (DPI, RGB888) on a custom board on am62.

How can I change the clock polarity of the data output to rising edge driven?

The following was confirmed:

1. Set "DRM_BUS_FLAG_PIXDATA_DRIVE_POSEDGE" to ".bus_flags" in struct panel_desc on panel-simple.c.

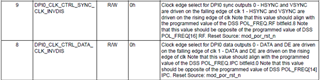

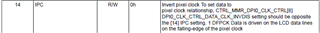

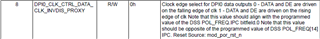

Result: IPC register is confirmed to be "0", but DPI0_CLK_CTRL_DATA_CLK_INVDIS is "0".

Shouldn't DPI0_CLK_CTRL_DATA_CLK_INVDIS be set to 1?

Read register values from Linux.

root@am62xx-custom:~# devmem2 0x3020B04C w /dev/mem opened. Memory mapped at address 0xffffafc72000. Read at address 0x3020B04C (0xffffafc7204c): 0x00063000 root@am62xx-custom:~# devmem2 0x00108300 w /dev/mem opened. Memory mapped at address 0xffffa1837000. Read at address 0x00108300 (0xffffa1837300): 0x00000000

The waveform is as follows: (CH1:CLK, CH2:DATA)

Data is output on the falling edge of the clock. In reality, data should be output on the rising edge of the clock.

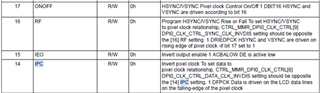

2.Set "DRM_BUS_FLAG_PIXDATA_DRIVE_NEGEDGE" to ".bus_flags" in struct panel_desc on panel-simple.c.

Result: IPC register is confirmed to be "1", but DPI0_CLK_CTRL_DATA_CLK_INVDIS is "0".

Read register values from Linux

root@am62xx-custom:~# devmem2 0x3020B04C w /dev/mem opened. Memory mapped at address 0xffff9f4a3000. Read at address 0x3020B04C (0xffff9f4a304c): 0x00067000 root@am62xx-custom:~# devmem2 0x00108300 w /dev/mem opened. Memory mapped at address 0xffff84d14000. Read at address 0x00108300 (0xffff84d14300): 0x00000000

The waveform is as follows:

Data is output on the falling edge of the clock. (CH1:CLK, CH2:DATA)

[Reference]

SoC: AM6251

Board: Custom board

SDK: PROCESSOR-SDK-LINUX-RT-AM62X (Version.09.02.01.10)

LCD: P0700WVN1MB00 (TIANMA)

Device Driver: panel-simple.c ("CONFIG_DRM_PANEL_SIMPLE)

# For LCD timing, add the following to panel-simple.c

@@ -4027,6 +4036,36 @@ static const struct panel_desc yes_optoelectronics_ytc700tlag_05_201c = {

.connector_type = DRM_MODE_CONNECTOR_LVDS,

};

+static const struct drm_display_mode tianma_P0700WVN1MB00_mode = {

+ .clock = 33300,

+ .hdisplay = 800,

+ .hsync_start = 800 + 210,

+ .hsync_end = 800 + 210 + 20,

+ .htotal = 800 + 210 + 20 + 26,

+ .vdisplay = 480,

+ .vsync_start = 480 + 22,

+ .vsync_end = 272 + 22 + 3,

+ .vtotal = 272 + 22 + 3 + 20,

+ .flags = DRM_MODE_FLAG_NVSYNC | DRM_MODE_FLAG_NHSYNC,

+};

+

+static const struct panel_desc tianma_P0700WVN1MB00 = {

+ .modes = &tianma_P0700WVN1MB00_mode,

+ .num_modes = 1,

+ .bpc = 8,

+ .size = {

+ .width = 154,

+ .height = 86,

+ },

+ .delay = {

+ .prepare = 25,

+ .enable = 100,

+ },

+ .bus_format = MEDIA_BUS_FMT_RGB888_1X24,

+ .bus_flags = DRM_BUS_FLAG_DE_LOW,

+ .connector_type = DRM_MODE_CONNECTOR_DPI,

+};

+

@@ -4456,6 +4495,9 @@ static const struct of_device_id platform_of_match[] = {

}, {

.compatible = "yes-optoelectronics,ytc700tlag-05-201c",

.data = &yes_optoelectronics_ytc700tlag_05_201c,

+ }, {

+ .compatible = "tianma,P0700WVN1MB00",

+ .data = &tianma_P0700WVN1MB00,

}, {

/* Must be the last entry */

.compatible = "panel-dpi",

Regards,

TO