Tool/software:

Hi,

i have a custom board with own yocto linux build. Right now i booting from sdcard. Looks good so far.

I trying porting pru1_0 code from am43 to am64. I can load and start different binary without any problem. /sys/class/remoteproc/remoteproc6/state print it is "running".

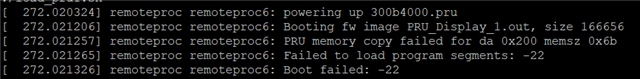

What i am observing is that the binary .out (elf-file) is more then double the size of am43 for the same code. Why? The final size of my binary is ~168KB. If i try to load and start the binary i am getting:

If i remove some code and the final binary i a lil bit smaller ~164K, i have not problem.

The map file looks ok:

******************************************************************************

PRU Linker Unix v2.3.3

******************************************************************************

>> Linked Wed Feb 12 16:56:59 2025

OUTPUT FILE NAME: <gen/PRU1/PRU_Display_1.out>

ENTRY POINT SYMBOL: "_c_int00_noinit_noargs" address: 00000000

MEMORY CONFIGURATION

name origin length used unused attr fill

---------------------- -------- --------- -------- -------- ---- --------

PAGE 0:

PRU_IMEM 00000000 00003000 00000834 000027cc RWIX

PAGE 1:

PRU1_DMEM_1 00000000 00001000 00000277 00000d89 RWIX

RTU1_DMEM_1 00001000 00000800 00000000 00000800 RWIX

TX_PRU1_DMEM_1 00001800 00000800 00000000 00000800 RWIX

PRU1_DMEM_0 00002000 00001000 00000000 00001000 RWIX

RTU1_DMEM_0 00003000 00000800 00000000 00000800 RWIX

TX_PRU1_DMEM_0 00003800 00000800 00000000 00000800 RWIX

PAGE 2:

PRU_RTU_RAT1 00009000 00000854 00000000 00000854 RWIX

PRU_SHAREDMEM 00010000 00010000 00000000 00010000 RWIX

PRU_INTC 00020000 00001504 00001504 00000000 RWIX

PRU1_CTRL 00024000 00000030 00000000 00000030 RWIX

RSVD14 00024800 00000100 00000000 00000100 RWIX

PRU_CFG 00026000 00000100 00000000 00000100 RWIX

PRU_CFG_0x100 00026100 00000098 00000000 00000098 RWIX

PA_STATS_QRAM 00027000 00001000 00000000 00001000 RWIX

PRU_UART 00028000 00000038 00000000 00000038 RWIX

TM_CFG_PRU1 0002a200 0000004c 00000000 0000004c RWIX

PA_STATS_CRAM 0002c000 00001000 00000000 00001000 RWIX

PRU_IEP0 0002e000 00000100 00000000 00000100 RWIX

PRU_IEP0_0x100 0002e100 0000021c 00000000 0000021c RWIX

PRU_IEP1 0002f000 00000100 00000000 00000100 RWIX

PRU_IEP1_0x100 0002f100 0000021c 00000000 0000021c RWIX

PRU_ECAP 00030000 00000060 00000000 00000060 RWIX

MII_RT 00032000 00000070 00000000 00000070 RWIX

MII_MDIO 00032400 00000088 00000000 00000088 RWIX

MII_G_RT 00033000 00000f44 00000000 00000f44 RWIX

RSVD15 60000000 00000100 00000000 00000100 RWIX

RSVD16 70000000 00000100 00000000 00000100 RWIX

RSVD17 80000000 00000100 00000000 00000100 RWIX

RSVD18 90000000 00000100 00000000 00000100 RWIX

RSVD19 a0000000 00000100 00000000 00000100 RWIX

RSVD20 b0000000 00000100 00000000 00000100 RWIX

RSVD23 c0000000 00000100 00000000 00000100 RWIX

RSVD29 d0000000 00010000 00000000 00010000 RWIX

RSVD30 e0000000 00010000 00000000 00010000 RWIX

RSVD31 f0000000 00010000 00000000 00010000 RWIX

SECTION ALLOCATION MAP

output attributes/

section page origin length input sections

-------- ---- ---------- ---------- ----------------

.text:_c_int00*

* 0 00000000 0000001c

00000000 0000001c rtspruv3_le.lib : boot.c.obj (.text:_c_int00_noinit_noargs)

.text 0 0000001c 00000818

0000001c 0000036c main.object (.text:DisplayLoop)

00000388 000000f0 spi.object (.text:SpiTxRx)

00000478 000000a8 spi.object (.text:SpiSetup)

00000520 000000a0 main.object (.text:SignalEvent)

000005c0 00000064 main.object (.text:CheckForRunStopTelegram)

00000624 0000005c main.object (.text:SetDefaultTeleV2)

00000680 0000005c main.object (.text:SetTextTeleV2)

000006dc 00000054 spi.object (.text:SpiReset)

00000730 00000048 main.object (.text:CheckForDefaultTelegram)

00000778 00000048 main.object (.text:main)

000007c0 00000034 rtspruv3_le.lib : memcpy.asm.obj (.text)

000007f4 00000030 crcfcts.object (.text:UtilCRC8)

00000824 00000008 rtspruv3_le.lib : exit.c.obj (.text:abort)

0000082c 00000008 : exit.c.obj (.text:loader_exit)

.stack 1 00000108 00000100 UNINITIALIZED

00000108 00000004 rtspruv3_le.lib : boot.c.obj (.stack)

0000010c 000000fc --HOLE--

.data 1 00000208 0000006f

00000208 00000058 main.object (.data:sReadBuf)

00000260 00000017 main.object (.data)

.cinit 1 00000000 00000000 UNINITIALIZED

.rodata 1 00000000 00000108

00000000 00000100 crcfcts.object (.rodata:.string:abyCRC8Tab)

00000100 00000008 main.object (.rodata:.string)

.creg.PRU_INTC.noload.near

* 2 00020000 00000000 NOLOAD SECTION

.creg.PRU_INTC.near

* 2 00020000 00000000 UNINITIALIZED

.creg.PRU_INTC.noload.far

* 2 00020000 00001504 NOLOAD SECTION

00020000 00001504 main.object (.creg.PRU_INTC.noload.far)

.creg.PRU_INTC.far

* 2 00021504 00000000 UNINITIALIZED

MODULE SUMMARY

Module code ro data rw data

------ ---- ------- -------

gen/PRU1/

main.object 1464 8 5491

spi.object 492 0 0

crcfcts.object 48 256 0

+--+----------------+------+---------+---------+

Total: 2004 264 5491

/home/chris/ti/ti-processor-sdk-linux-rt-am64xx-evm-10.00.07.04/linux-devkit/sysroots/x86_64-arago-linux/usr/share/ti/cgt-pru//lib/rtspruv3_le.lib

memcpy.asm.obj 52 0 0

boot.c.obj 28 0 0

exit.c.obj 16 0 0

+--+----------------+------+---------+---------+

Total: 96 0 0

Stack: 0 0 256

+--+----------------+------+---------+---------+

Grand Total: 2100 264 5747

SEGMENT ATTRIBUTES

id tag seg value

-- --- --- -----

0 PHA_PAGE 1 1

1 PHA_PAGE 2 1

2 PHA_PAGE 3 1

GLOBAL SYMBOLS: SORTED ALPHABETICALLY BY Name

page address name

---- ------- ----

0 0000082c C$$EXIT

2 00020000 CT_INTC

0 000006dc SpiReset

0 00000478 SpiSetup

0 00000388 SpiTxRx

0 000007f4 UtilCRC8

abs 00033000 __PRU_CREG_BASE_MII_G_RT

abs 00032400 __PRU_CREG_BASE_MII_MDIO

abs 00032000 __PRU_CREG_BASE_MII_RT

abs 0002c000 __PRU_CREG_BASE_PA_STATS_CRAM

abs 00027000 __PRU_CREG_BASE_PA_STATS_QRAM

abs 00024000 __PRU_CREG_BASE_PRU1_CTRL

abs 00002000 __PRU_CREG_BASE_PRU1_DMEM_0

abs 00000000 __PRU_CREG_BASE_PRU1_DMEM_1

abs 00026000 __PRU_CREG_BASE_PRU_CFG

abs 00026100 __PRU_CREG_BASE_PRU_CFG_0x100

abs 00030000 __PRU_CREG_BASE_PRU_ECAP

abs 0002e000 __PRU_CREG_BASE_PRU_IEP0

abs 0002e100 __PRU_CREG_BASE_PRU_IEP0_0x100

abs 0002f000 __PRU_CREG_BASE_PRU_IEP1

abs 0002f100 __PRU_CREG_BASE_PRU_IEP1_0x100

abs 00020000 __PRU_CREG_BASE_PRU_INTC

abs 00009000 __PRU_CREG_BASE_PRU_RTU_RAT1

abs 00010000 __PRU_CREG_BASE_PRU_SHAREDMEM

abs 00028000 __PRU_CREG_BASE_PRU_UART

abs 00024800 __PRU_CREG_BASE_RSVD14

abs 60000000 __PRU_CREG_BASE_RSVD15

abs 70000000 __PRU_CREG_BASE_RSVD16

abs 80000000 __PRU_CREG_BASE_RSVD17

abs 90000000 __PRU_CREG_BASE_RSVD18

abs a0000000 __PRU_CREG_BASE_RSVD19

abs b0000000 __PRU_CREG_BASE_RSVD20

abs c0000000 __PRU_CREG_BASE_RSVD23

abs d0000000 __PRU_CREG_BASE_RSVD29

abs e0000000 __PRU_CREG_BASE_RSVD30

abs f0000000 __PRU_CREG_BASE_RSVD31

abs 0002a200 __PRU_CREG_BASE_TM_CFG_PRU1

abs 00000009 __PRU_CREG_MII_G_RT

abs 00000015 __PRU_CREG_MII_MDIO

abs 0000001b __PRU_CREG_MII_RT

abs 0000000d __PRU_CREG_PA_STATS_CRAM

abs 0000000c __PRU_CREG_PA_STATS_QRAM

abs 0000000b __PRU_CREG_PRU1_CTRL

abs 00000019 __PRU_CREG_PRU1_DMEM_0

abs 00000018 __PRU_CREG_PRU1_DMEM_1

abs 00000004 __PRU_CREG_PRU_CFG

abs 00000005 __PRU_CREG_PRU_CFG_0x100

abs 00000003 __PRU_CREG_PRU_ECAP

abs 0000001a __PRU_CREG_PRU_IEP0

abs 00000008 __PRU_CREG_PRU_IEP0_0x100

abs 00000001 __PRU_CREG_PRU_IEP1

abs 00000002 __PRU_CREG_PRU_IEP1_0x100

abs 00000000 __PRU_CREG_PRU_INTC

abs 00000016 __PRU_CREG_PRU_RTU_RAT1

abs 0000001c __PRU_CREG_PRU_SHAREDMEM

abs 00000007 __PRU_CREG_PRU_UART

abs 0000000e __PRU_CREG_RSVD14

abs 0000000f __PRU_CREG_RSVD15

abs 00000010 __PRU_CREG_RSVD16

abs 00000011 __PRU_CREG_RSVD17

abs 00000012 __PRU_CREG_RSVD18

abs 00000013 __PRU_CREG_RSVD19

abs 00000014 __PRU_CREG_RSVD20

abs 00000017 __PRU_CREG_RSVD23

abs 0000001d __PRU_CREG_RSVD29

abs 0000001e __PRU_CREG_RSVD30

abs 0000001f __PRU_CREG_RSVD31

abs 0000000a __PRU_CREG_TM_CFG_PRU1

1 00000208 __TI_STACK_END

abs 00000100 __TI_STACK_SIZE

abs ffffffff __c_args__

0 00000000 _c_int00_noinit_noargs

1 00000108 _stack

0 00000824 abort

0 00000778 main

0 000007c0 memcpy

GLOBAL SYMBOLS: SORTED BY Symbol Address

page address name

---- ------- ----

0 00000000 _c_int00_noinit_noargs

0 00000388 SpiTxRx

0 00000478 SpiSetup

0 000006dc SpiReset

0 00000778 main

0 000007c0 memcpy

0 000007f4 UtilCRC8

0 00000824 abort

0 0000082c C$$EXIT

1 00000108 _stack

1 00000208 __TI_STACK_END

2 00020000 CT_INTC

abs 00000000 __PRU_CREG_BASE_PRU1_DMEM_1

abs 00000000 __PRU_CREG_PRU_INTC

abs 00000001 __PRU_CREG_PRU_IEP1

abs 00000002 __PRU_CREG_PRU_IEP1_0x100

abs 00000003 __PRU_CREG_PRU_ECAP

abs 00000004 __PRU_CREG_PRU_CFG

abs 00000005 __PRU_CREG_PRU_CFG_0x100

abs 00000007 __PRU_CREG_PRU_UART

abs 00000008 __PRU_CREG_PRU_IEP0_0x100

abs 00000009 __PRU_CREG_MII_G_RT

abs 0000000a __PRU_CREG_TM_CFG_PRU1

abs 0000000b __PRU_CREG_PRU1_CTRL

abs 0000000c __PRU_CREG_PA_STATS_QRAM

abs 0000000d __PRU_CREG_PA_STATS_CRAM

abs 0000000e __PRU_CREG_RSVD14

abs 0000000f __PRU_CREG_RSVD15

abs 00000010 __PRU_CREG_RSVD16

abs 00000011 __PRU_CREG_RSVD17

abs 00000012 __PRU_CREG_RSVD18

abs 00000013 __PRU_CREG_RSVD19

abs 00000014 __PRU_CREG_RSVD20

abs 00000015 __PRU_CREG_MII_MDIO

abs 00000016 __PRU_CREG_PRU_RTU_RAT1

abs 00000017 __PRU_CREG_RSVD23

abs 00000018 __PRU_CREG_PRU1_DMEM_1

abs 00000019 __PRU_CREG_PRU1_DMEM_0

abs 0000001a __PRU_CREG_PRU_IEP0

abs 0000001b __PRU_CREG_MII_RT

abs 0000001c __PRU_CREG_PRU_SHAREDMEM

abs 0000001d __PRU_CREG_RSVD29

abs 0000001e __PRU_CREG_RSVD30

abs 0000001f __PRU_CREG_RSVD31

abs 00000100 __TI_STACK_SIZE

abs 00002000 __PRU_CREG_BASE_PRU1_DMEM_0

abs 00009000 __PRU_CREG_BASE_PRU_RTU_RAT1

abs 00010000 __PRU_CREG_BASE_PRU_SHAREDMEM

abs 00020000 __PRU_CREG_BASE_PRU_INTC

abs 00024000 __PRU_CREG_BASE_PRU1_CTRL

abs 00024800 __PRU_CREG_BASE_RSVD14

abs 00026000 __PRU_CREG_BASE_PRU_CFG

abs 00026100 __PRU_CREG_BASE_PRU_CFG_0x100

abs 00027000 __PRU_CREG_BASE_PA_STATS_QRAM

abs 00028000 __PRU_CREG_BASE_PRU_UART

abs 0002a200 __PRU_CREG_BASE_TM_CFG_PRU1

abs 0002c000 __PRU_CREG_BASE_PA_STATS_CRAM

abs 0002e000 __PRU_CREG_BASE_PRU_IEP0

abs 0002e100 __PRU_CREG_BASE_PRU_IEP0_0x100

abs 0002f000 __PRU_CREG_BASE_PRU_IEP1

abs 0002f100 __PRU_CREG_BASE_PRU_IEP1_0x100

abs 00030000 __PRU_CREG_BASE_PRU_ECAP

abs 00032000 __PRU_CREG_BASE_MII_RT

abs 00032400 __PRU_CREG_BASE_MII_MDIO

abs 00033000 __PRU_CREG_BASE_MII_G_RT

abs 60000000 __PRU_CREG_BASE_RSVD15

abs 70000000 __PRU_CREG_BASE_RSVD16

abs 80000000 __PRU_CREG_BASE_RSVD17

abs 90000000 __PRU_CREG_BASE_RSVD18

abs a0000000 __PRU_CREG_BASE_RSVD19

abs b0000000 __PRU_CREG_BASE_RSVD20

abs c0000000 __PRU_CREG_BASE_RSVD23

abs d0000000 __PRU_CREG_BASE_RSVD29

abs e0000000 __PRU_CREG_BASE_RSVD30

abs f0000000 __PRU_CREG_BASE_RSVD31

abs ffffffff __c_args__

[76 symbols]

Could you please help me to analyze?

Thanks a lot

Chris