Other Parts Discussed in Thread: TLV320AIC3101

Tool/software:

Test method:

In order to test if failed device on I2C bus hang system, created a test scenario to access 1 existing device and 1not existing device in alternatively.

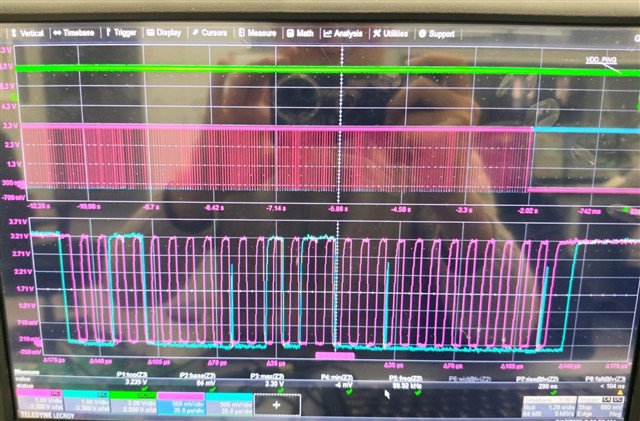

#1. In normal case, the wave form as below (there is data stage after sending out slave address and ACK):

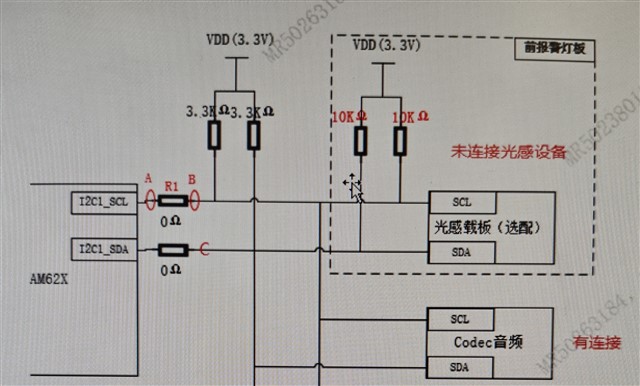

#2. Fail waveform as below, after sending out address to existing device, the bus was hold after address and ACK stage as below. it should be data stage as upper normal access.

#3. It can be reproduced certainly from 1 hours to 14 hours.

#4. Captured 4 times failure, all happened at accessing existing device after address stage as upper captured waveform,

#5. Test with 2 existing device accessing, did not reproduce the failure so far.

Analysis:

#1. Did experiments to replace serial resistor with wire, disconnect wire after reproduced to probe on either side, SCL is low on AM62x side, SCL is high on slave side, at least it prove SCL is not hold by slave.

#2. After I2C bus hang, I2C1_SYSTEST register value is 0x60, software detected BUSY and return.

#3. Write I2C_SYSC[SRST] can resume the bus, but it is more easy to re-produce again.