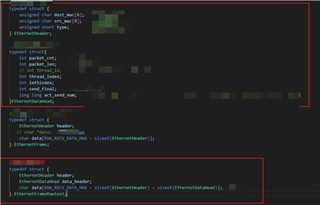

Tool/software:

icssg dirver: porting from uboot in sdk9.0

test method: phy internal loopback

compile chain: gcc

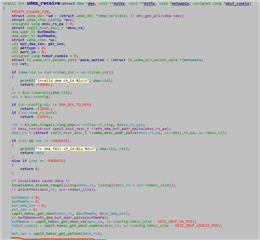

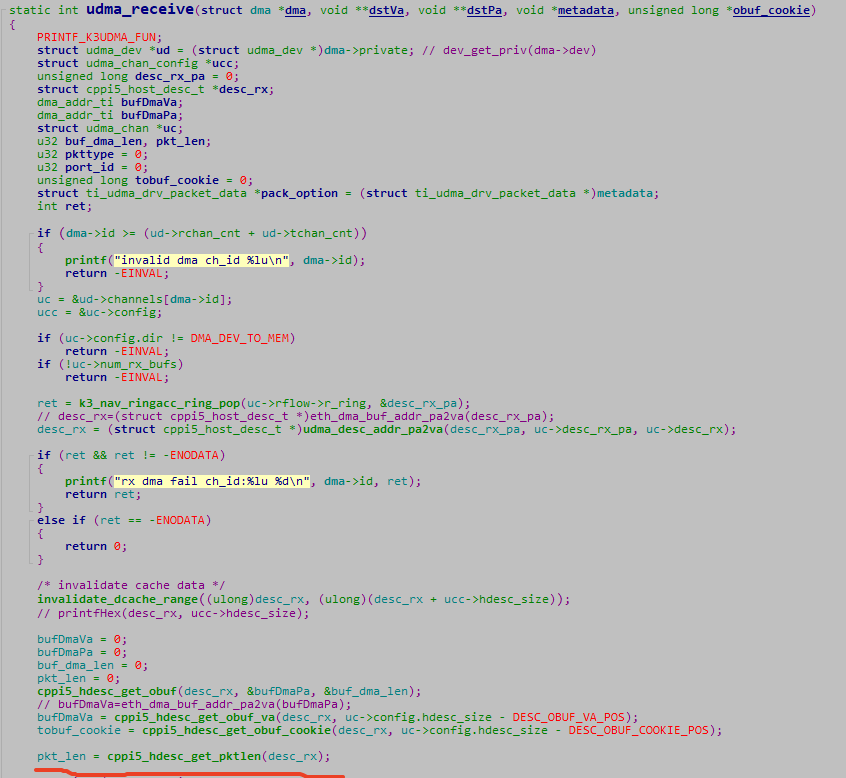

When testing RAW data, send 1024 bytes of data every 1ms, receive the data, and check the receive length, which can sometimes be 1532.

Read the statistics register of the MII_G module to show that the total data length received can be evenly divided by the length of each packet, that is, the length of the data received by the MII_G module is no problem.

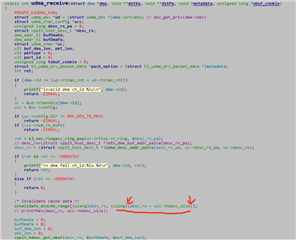

There is a problem with the pru module receiving data and then transmitting it to DMA.

What is the cause of this problem and how can I solve it.