Tool/software:

Hi TI,

I am developing my own cpsw2g driver using bare metal.

I have a few questions about CPSW2G Tx Priority queues which are as follows:

- What are Tx Priority queues?

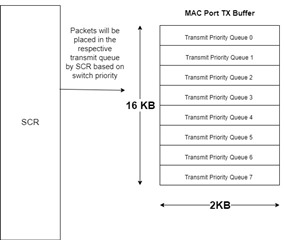

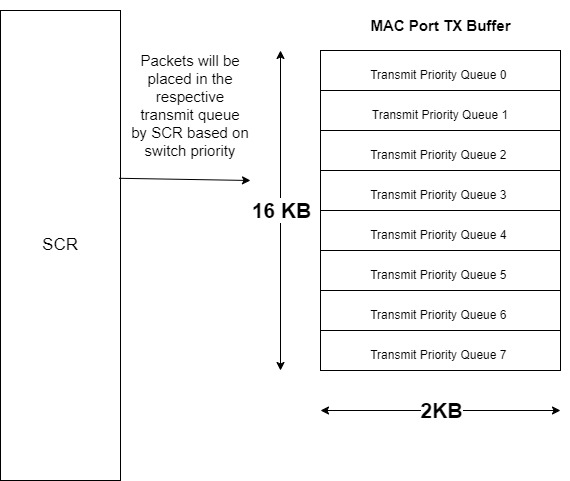

- How are they allocated inside MAC Port FIFO?

Are these HW components and physically mapped inside MAC Port FIFO? - Who is responsible for putting the data in Tx Priority queues from MAC Port Tx FIFO?

- Consider a case that I have allocated 16 KB for Tx MAC Port Buffer. and I have allocated 2KB for Tx Priority queue 0.

Is the remaining size allocated for Tx MAC Port Buffer is now 14 KB (16 KB - 2 KB) or Tx MAC Port Buffer is still 16 KB and it is not related to the size of Tx Priority queues?

Looking forward to hearing back from you.

Best Regards,

Hasan