Tool/software:

Hello TI,

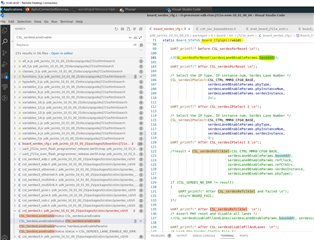

When we have Old Linux SDK (7.3) we upgraded to 10.1 RTOS SDK for MCU2_0 and MCU2_1 there everything working fine, but when we upgraded to new Linux SDK (10.1), we see that SGMII ports not able to initialize, so what could be the issue ?

Thanks and Regards,

Satya.