Tool/software:

Hi,

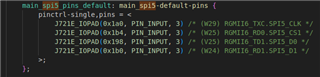

I need to configure SPI5 in the Linux device tree. Currently, I am using the configuration shown in the figure below. I would like to know if SPI5 pins still need to be configured in path pdk_jacinto_10_00_00_27/packages/ti/board/src/j721e_evm/J721E_pinmux_data.c?

Besides, I used CS1 in SPI5, should the parameter 'reg=<0>' be modified to 'reg=<1>'? What does this parameter mean?

Regards,

Yang