Tool/software:

Is it possible to use SGMII interfaces from the SoC without additional 100MHz external reference clock source, so that the only clock input to the SoC would be the oscillator at WKUP_OSC0?

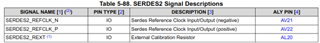

In EVM design (PROC141E5) on the SoC schematics symbol both the PCIE_REFCLK0 and PCIE_REFCLK2 outputs are associated with SERDES1 block.

Can I use for example PCIE_REFCLK2 output to clock SGMII5 and -7 interfaces from SERDES2?

Can any PCIE_REFCLKx outputs be associated with any SERDESx?