Tool/software:

Hi community,

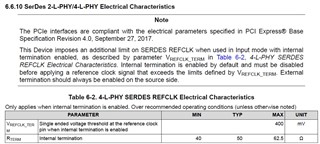

My question is about SERDES_REFCLK input pins. There are some constraints mentioned in the datasheet that I don't understand at all

- It is said that an internal termination exists by default. I guess that default means "at power up" .

- is this Correct ?

- If we use SERDES for booting purpose, for example PCIE, or else this requires SERDES_REFCLK to be alive before SOC starts executing ROM code.

- Is this Correct ?

- Therefore we MUST respect the table 6-2. The problem is that I don't understand the meaning of "threshold" in that case.

- Does this mean that none of the _P and _N signals should exceed 400mV ? which would limit peak-to-peak differential voltage to a very small quantity, for example Vol=0.1V and Voh=0.3V

- Does this mean that _P must be >0.4V (while N_being < 0.4V) in order to be seen as '1' ?

- It is not clear to which characteristic this constraint applies to. Could you explain please.

- The table introduces the internal RTERM value. I guess that this refers to the load that each _P and _N signal sees.

- Is this correct ?

- I understand that the internal termination can be disabled.

- How is this performed ?

With best regards,

Bruno