Other Parts Discussed in Thread: AM62L, SYSCONFIG

Tool/software:

Hi,

Where can I find the list of module ID's and list of clocks? Seems not clickable like what Am62x does

Thanks,

Dazong

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Tool/software:

Hi,

Where can I find the list of module ID's and list of clocks? Seems not clickable like what Am62x does

Thanks,

Dazong

Hello Dazong,

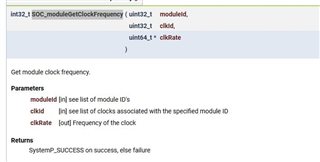

The above API is used to get clock frequency for all peripherals Modules .

So, if you want to know any peripheral operating frequency, then you simply need to pass the Module ID and Clock ID.

The operating frequency result should be available in the clockrate variable.

Typically we need to add these details to the SCI documentation. I need to check these details.

Currently, please use the file below to get clock ID and Peripheral IDs.

C:\ti\freertos_sdk_am62lx_11_00_00_05\source\drivers\scp\scmi\soc\am62lx

Regards,

Anil.

Dazong,

The link below is helpful to get the details about the peripheral runs at which is frequencies.

Regards,

Anil.

Thanks Anil,

The module I am trying to get frequency is LPDDR4.

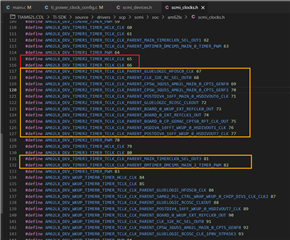

I am able to find the module id AM62LX_DEV_DDR16SS0

but seems clock id is not available yet when search ddr4 as keyword in the scmi_clocks.c file

Could you please confirm?

Thanks,

Dazong

Hello Dazong,

I could not able to find the DDR ID and I feel that this DDR ID is not available in the software due to the ROM bootloader is already initialized the DDR and users don't need to touch the DDR init again.

Try using the Clock ID as 0 and 1 check the frequency values you are getting.

Do you want to confirm whether the DDR is running at the proper frequency or not ?

Or do you want to read the DDR frequency in the software? Is this your requirement ?

Regards,

Anil.

Hi Anil,

The first several lines of our HW validation sw will print the modules frequency to so we can make sure they are running at correct speed.

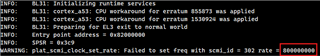

We read 25MHz with AM62LX_DEV_DDR16SS0 with clk value to be 0, and 1, which seems wrong. Could you please check this value on your side? We are using the tiboot3.bin from the SDK.

SOC_moduleGetClockFrequency(AM62LX_DEV_DDR16SS0, 0, &clkrate)

SOC_moduleGetClockFrequency(AM62LX_DEV_DDR16SS0, 1, &clkrate)

Thanks,

Dazong

Hello Dazong,

I hope there are no problems with other peripherals.

I suspect there is an issue with the CLOCK ID to get the DDR frequency and I can internally check with the team and let you know.

Regards,

Anil.

Hello Dazong,

I have verified with the internal team.

The request to SCM core to get the DDR clock frequency there are some issues on the SCM core side.

So, we don't support this request, and as of now there are no pans to support this issue .

Now, please skip this request and go ahead for other peripherals.

And, let me know if this reading DDR frequency is not met, will it create an impact on your application?

Please let me know if you face any issues other than the DDR.

Regards,

Anil.

Hi Anil,

With HW validation we want to make sure all peripherals are at correct clk freq and reading from sw is the most direct/easy way to do so. Could you suggest another way that I can verify lpddr4 freq?

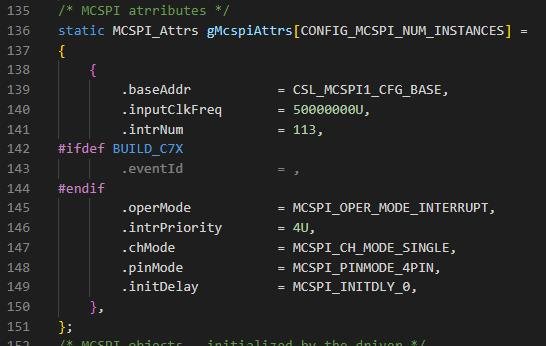

SPI freq shows 25MHz too where we set it to

Thanks,

Dazong

Hello Dazong,

For the DDR, I can check with internal experts how to confirm the DDR is operating at which frequency ?

For the SPI, it seems you have configured the 50MHz clock on the 140th line, but after the SCI Free request have you still seen the 25MHz clock ?

Is this the issue ?

Regards,

Anil.

Hi Anil,

this SPI input clk at 25MHz is also from SOC_moduleGetClockFrequency()

SOC_moduleGetClockFrequency(AM62LX_DEV_MCSPI1, 0, &clkRate);

Thanks,

Dazong

Hello Dazong,

Please use the link below to pass the Clock IDs to get the particular Peripheral frequency.

Try with 302 instead of 0 and see if you are able to get the 50MHz clock.

https://github.com/TexasInstruments/arm-trusted-firmware/blob/ti-master/docs/plat/ti-am62l.rst

Regards,

Anil.

Hello Dazong,

To verify the DDR frequency on the AM62L SOC, I have identified two possible software methods. Below is a detailed explanation of each method .

Method 1: Monitoring DDR PLL Input Usage in Other Peripherals

Approach:

• The DDR PLL input clock is used by multiple peripherals (e.g., timers, other high-speed interfaces).

• If any peripheral shares this clock, we could monitor that peripheral’s clock configuration .

• In AM62L, the DDR PLL input clock is not shared with any other IPs—it is dedicated only to the DDR subsystem.

Since no other peripheral can provide an indirect way to monitor the DDR frequency, this method is not applicable.

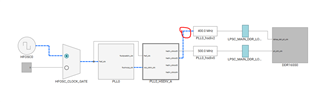

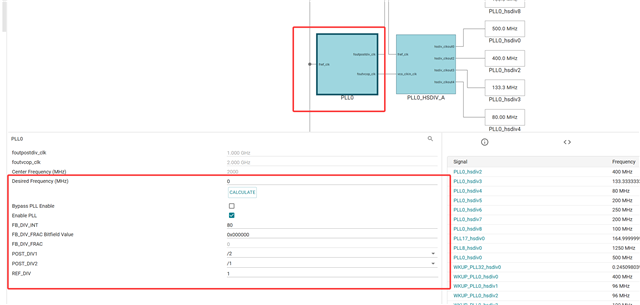

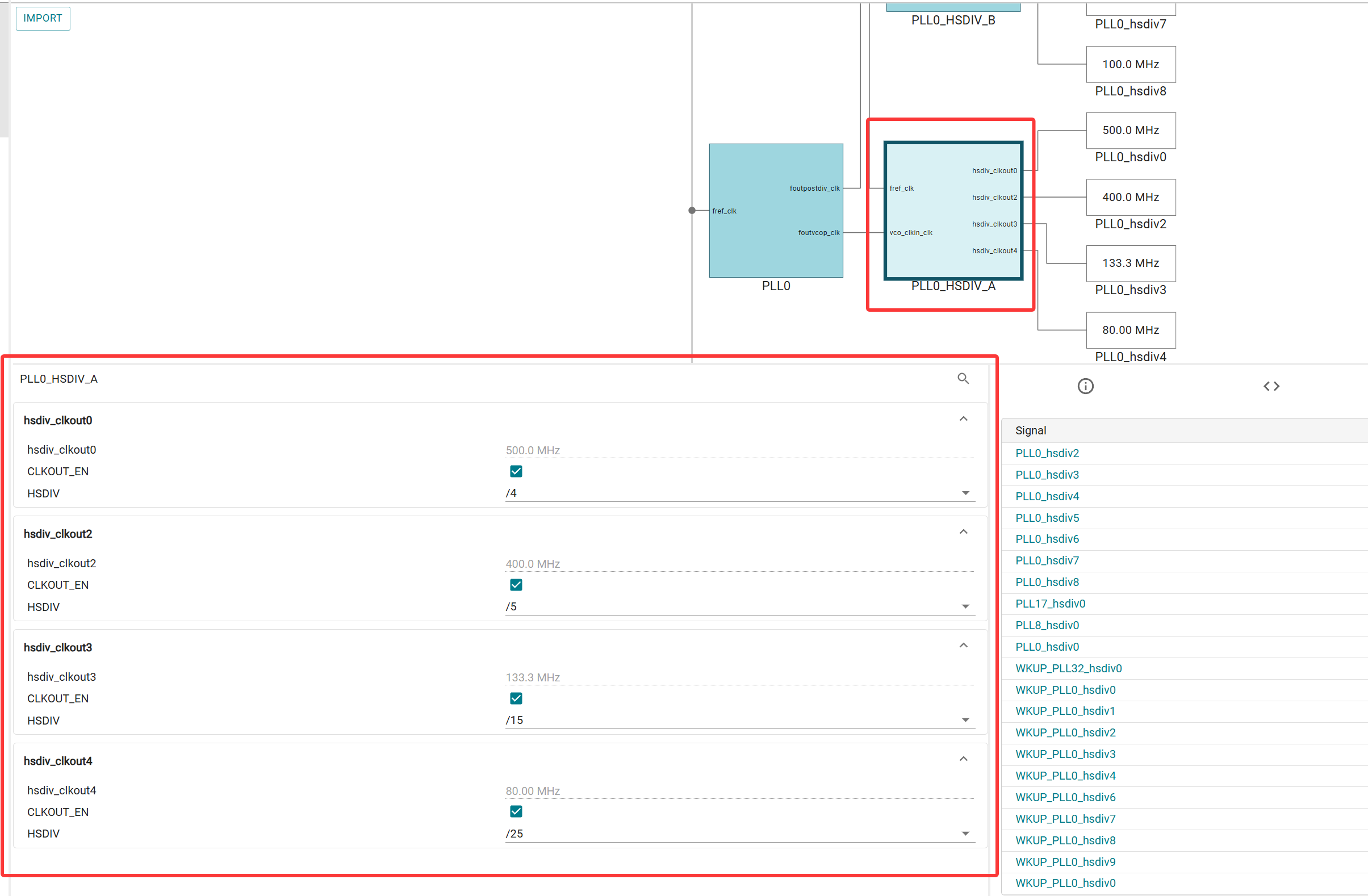

Method 2: Checking PLL Scaling Factors from Input to DDR Output Clock

Approach:

• Instead of monitoring another IP, we check the clock tree configuration to determine the DDR frequency.

• The input clock to the PLL is 25MHz, which passes through the PLLHSDIVA block to generate the DDR frequency.

• The key parameter to monitor is HSDIVCLKOUT2, which is responsible for providing the final DDR clock.

• By reading the scaling factor of HSDIVCLKOUT2, we can confirm if the expected frequency is being generated.

Implementation in AM62L:

1. The DDR PLL receives a 25MHz input clock.

2. The PLLHSDIVA block scales this input using a divider (HSDIVCLKOUT2).

3. The expected scaling factor is 5, which results in a DDR clock of 25MHz × 5 = 400MHz.

4. By checking if the HSDIVCLKOUT2 scaling factor is set to 5, we can confirm that the DDR is running at 400MHz.

Please make sure that , you are not supposed to set any values in that register which will impact to the DDR .

Regards,

Anil.

Hi Anil,

I am a little busy handling another task right now, I will give a try later this week and update you.

Thank you,

Dazong

Hello Dazong,

I am not closing this thread and open for your feedback..

Regards,

Anil.

Hi Anil,

With boot from USB, is the DDR clock initialized in TF-A stage or later one?

Thanks,

Dazong

Hello Dazong,

The DDR clock init and config is done in Stage 1 in TF - A stage only.

You can please look at these details below.

Regards,

Anil.

Hi Anil,

1) As discussed in the meeting, let me know what Ti seems from the input clk freq of DDR4.

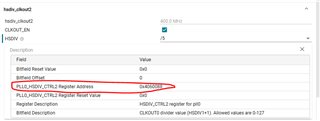

Based on your suggested way to read values, I am getting

FB_DIV_INT = 80

hsdiv = 4

so I think it is running at 500MHz.

2) in the meeting I talked about the I2C clk freq issue. Since we are implementing modules one by one. Do you want me to test all modules and provide all matter in once, or you want me to update this module by module

Thanks,

Dazong

Hello Dazong,

in the meeting I talked about the I2C clk freq issue. Since we are implementing modules one by one. Do you want me to test all modules and provide all matter in once, or you want me to update this module by module

Yes, the above one makes sense and complete test for all the modules and share all the details in a single comment which are not working.

We can fix them in a single shot.

hsdiv = 4

so I think it is running at 500MHz.

Can you please confirm which is the register address you are reading ?

Regards,

Anil.

Hi Anil,

The values are read from

1) As discussed in the meeting, let me know what Ti seems from the input clk freq of DDR4.

Based on your suggested way to read values, I am getting

FB_DIV_INT = 80

hsdiv = 4so I think it is running at 500MHz.

Hello Dazong,

Based on the clock configuration and test results:

• The Active HSDIV value is set to 4.

• In the clock tree calculation, the formula used is:

Effective Divider = HSDIV + 1,

so the actual divider becomes 5.

• Given the base frequency, the resulting DDR input clock is:

Base Frequency / 5 = 400 MHz.

Within the DDRSS (DDR Subsystem):

• The DDR PHY and EMIF modules internally multiply the 400 MHz clock by 2, resulting in an 800 MHz DDR clock.

• Since DDR (Double Data Rate) transfers data on both the rising and falling edges of the clock, the effective data rate becomes:

800 MHz × 2 = 1600 MT/s (Mega Transfers per second).

Regards,

Anil.

Thanks for the detailed explanation, Anil!

Could you please let me kow where I can find this info, I checked TRM but was not able to find. "The DDR PHY and EMIF modules internally multiply the 400 MHz clock by 2, resulting in an 800 MHz DDR clock"

Thank you,

Dazong

Hello Dazong,

Yes, this information is not currently mentioned in the TRM.

However, I have referred to the AM62L Clock IP Specification document, and according to that, the DDRSS output clock is fixed at 800 MHz.

Unfortunately, I’m unable to share this internal document with you, but for your reference ,you can consider the DDRSS output as always operating at 800 MHz.

I will also check with the hardware experts to see how we can incorporate this detail into the TRM in future revisions.

Regards,

Anil.

Hi Anil,

We've probed the LPDDR4 clk and verified that it is running at 800MHz.

Yes it would be great if this information " multiply the 400 MHz clock by 2," can be included into TRM.

I plan to keep this ticket open till we confirm that we can read clk for all the modules we use. Let me know if you think otherwise.

Thanks,

Dazong

Hello Dazong,

I am not closing this thread.

Please share all the details whenever you face any issue while reading the peripheral clock frequency.

Best regards,

Anil

Hi Anil,

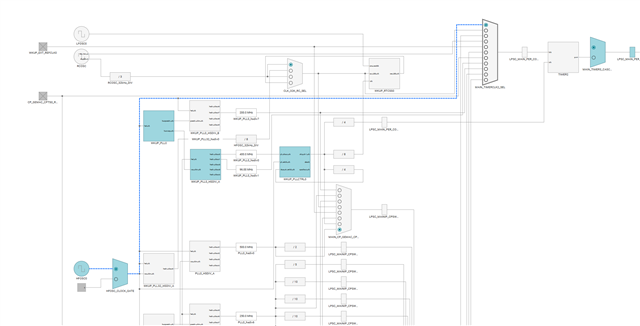

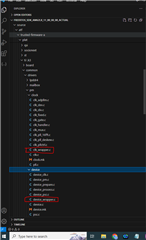

I am analyzing TF-A now. Could you please verify if I am looking at the correct file for clock settings.

plls: ti-processor-sdk-linux-am62lxx-evm-11.00.00.03\board-support\trusted-firmware-a-2.11+git\plat\ti\k3\am62l\scmi\drivers\soc\am62lx\clocks.c

periphrals: ti-processor-sdk-linux-am62lxx-evm-11.00.00.03\board-support\ti-u-boot-2024.10+git\dts\upstream\src\arm64\ti\k3-am62l-main.dtsi

Any other files I should look into? What I am trying to achieve is make sure the clock setting, then I will put the values into

With the visual output from the website, compare the result from SOC_ModuelGetClockFrequency()

For exmaple these fields

I am not sure if periprhals are set from uboot when boot from USB DFU

Thanks,

Dazong

Hello Dazong,

Please look at the flow of the SCMI call.

The Application requests the clock set or gets PSC on or off for the particular IPs.

This request is written in the Shared memory next the control is jumped to the ATF.

The ATF will decide whether the particular operation is performed either it is clock-set or get or PSC on or off.

So, in the ATF folder first level you can check these wrapper files.

The ATF request these calls to perform clock setting or PSC ON and OFF as well.

int32_t SOC_moduleGetClockFrequency(uint32_t moduleId, uint32_t clkId, uint64_t *clkRate);

To get the clock ID, we need to pass Module ID and clock ID, which are available in these below.h files.

So, you need to use these files to get the particular IP frequencies.

All PLL settings are done by the ROM bootloader and again user don't need to touch them.

I am not sure if you are trying to update or reconfigure different PLL settings ?

Why do you want to change the PLL settings ?

Please let me know, the above replies cleared your queries.

Regards,

Anil.

Hi Anil,

We have two questions:

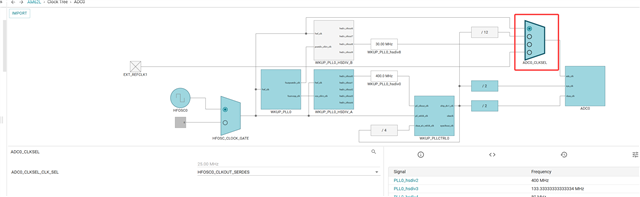

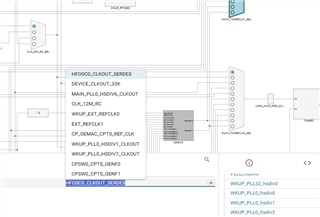

1) We are trying to set the clock frequency for Timer module (Timer 2 and 3) using the gSocModulesClockFrequency[] inside ti_power_clock_config.c. We couldn't get the TFA to boot successfully when we use select clocks like HFOSC0_CLKOUT_SERDE shown in sysconfig below:

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ AM62LX_DEV_TIMER2, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },

//{ AM62LX_DEV_TIMER3, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

a) How can we get this to work?

b) Where are the two clocks marked in red coming from?

c) Timer 3 doesn't have the 11 clocks mux options like Timer 2 has, are they connected internally?

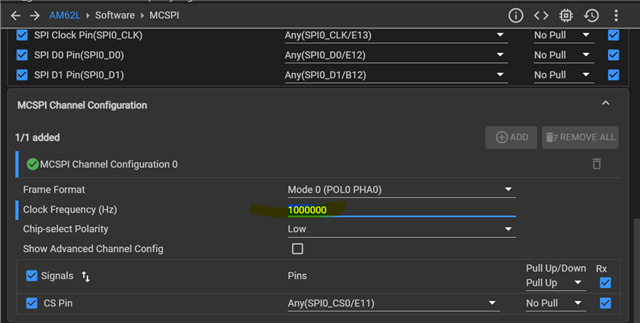

2) We also tried to set different frequency for MCSP1 using the snippet below.

SOC_ModuleClockFrequency gSocModulesClockFrequency[] = {

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 2400000000 },

{ SOC_MODULES_END, SOC_MODULES_END, SOC_MODULES_END },

};

However, we noticed that tfa booting failed to complete when certain clock frequencies were used e.g. 2.4GHz, 1000MHz, 800MHz, 700MHz, 500MHz etc.

While other frequencies like 1.2GHz, 600MHz, 400MHz, 300MHz, 200MHz seems to work.

What's responsible for that?

Best,

Simeon

a) How can we get this to work?

Hello Simeon,

All timers in the SoC have a MUX selection mechanism for their input clock source.

Timer Clock (TCLK) Source

• The TCLK refers to the Timer input clock, which is derived from the output of the clock MUX.

• For example, to select HFOSC as the input clock for TIMER2, the parameter below is correct:

AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK

/* ----------- TimerP ----------- */

#define CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR (0x9117000u)

#define CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT (0x0u)

/* set timer clock source */

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 2);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 2);

Hi Anil,

What we are studying is still the input clock to the peripherals.

The file we are play around with is ti_power_clock_config.c

uint32_t gSocModules[]; SOC_ModuleClockFrequency gSocModulesClockFrequency[]; void Module_clockEnable(void);

{ AM62LX_DEV_TIMER2, AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK, 25000000 },2. When play with MCSPI input clock freq, we observed it can be set to other values than 50MHz, like 100MHz, and SOC_ModuleGetClockFrequency() will also return 100MHz. my guess is the hsdiv_clkout6 is doing something as division can be set from /1 to /128. We are trying some values like up to 2.4GHz

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 2400000000 },

As Simeon mentioned, "frequencies like 1.2GHz, 600MHz, 400MHz, 300MHz, 200MHz seems to work". "clock frequencies were used e.g. 2.4GHz, 1000MHz, 800MHz, 700MHz, 500MHz etc. will fail"

{ AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, 600000000 },

SOC_moduleGetClockFrequency(AM62LX_DEV_MCSPI1, AM62LX_DEV_MCSPI1_CLKSPIREF_CLK, &clkRate);

info("MCSPI1 CLK RATE: %d\n", clkRate);

Print: MCSPI1 CLK RATE: 600000000

I guess ultimately it is two questions.

1. If we want to change the value of HSDIV, is it recommend to direct change the register itself using CSL_REG32_WR()?

2. If we want to change the mux input, like the case of timer2, why a valid parent clock name AM62LX_DEV_TIMER2_TIMER_TCLK_CLK_PARENT_GLUELOGIC_HFOSC0_CLK is not working, the whole application just stuck

Thanks,

Dazong

Hi Anil,

After trying direct MUX register configuration for timer, I don't see clock freq changes, still getting 100MHz. With CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT I think it should be 25Mhz since it is directly coming from HFO?

SOC_controlModuleUnlockMMR(SOC_DOMAIN_ID_MAIN, 2);

*(volatile uint32_t*)AddrTranslateP_getLocalAddr(CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT;

SOC_controlModuleLockMMR(SOC_DOMAIN_ID_MAIN, 2);

TIMER CLK RATE: 100000000

Thank you,

Dazong

After trying direct MUX register configuration for timer, I don't see clock freq changes, still getting 100MHz. With CONFIG_TIMER0_CLOCK_SRC_MUX_ADDR) = CONFIG_TIMER0_CLOCK_SRC_HFOSC0_CLKOUT I think it should be 25Mhz since it is directly coming from HFO?

Hello Dazong,

Yes, the above Mux setting is HFOSC clock. The Timer runs at 25MHz only and not 100MHz.

Can you please confirm how did you confirm the Timer Runs at 100MHz?

Did you read from the ATF ?

Regards,

Anil.

Hello Dazong,

With the current MUX settings, the timer is running at 25 MHz. I recommend configuring the timer to generate a 10 ms interrupt and then verifying the actual interrupt interval to confirm the behavior.

SOC_moduleGetClockFrequency

It appears that the SCMI clock frequency call is returning incorrect values. This is because the timer frequency is not set via MUX selection through the SCMI interface. As a result, ATF is unaware of the prescaler settings configured at the application level and therefore responds with default values.

For certain peripherals like (I2C,SPI,etc) , ATF gives the functional clock (FCLK) rates , and any further clock division happens at the IP level using prescaler configurations then you might receive the FCLK rather than the actual frequency that the peripheral is operating at.

My proposal:

Always retrieve the base frequency (FCLK) of the IP from ATF, and then read the prescaler settings of the IP. Using both values will give you the accurate effective clock rate of the peripheral.

Regards,

Anil.

I will give a try Anil,

From baremetal application, If I want to change hsdiv, should I direct write to register?

I guess the best way to set all the clock info is either in ATF or BSL. If want to do so, which file in ATF should I modify?

Thanks,

Dazong

Hello Dazong,

Before making any changes, please confirm which HSDIV you’re planning to modify.

This is critical because modifying an HSDIV affects multiple IPs, and an incorrect change can lead to system performance degradation.

Important Considerations:

• HSDIV changes impact all clock consumers using that output.

• If your SoC’s PLL feeds several peripherals via the same HSDIV, changing its divider can unintentionally slow down multiple modules.

About ATF and Clock Control:

• ATF does not expose straightforward APIs.

• It uses SCMI (System Control and Management Interface) for all device control operations (like clocks, resets, and power domains).

SCMI Clock & PSC Control Flow:

1. The application writes a message into the SCMI shared memory.

2. The application issues an SMC (Secure Monitor Call) to invoke ATF. Here, the application is stops and jump to the ATF code .

3. Inside ATF, the message is parsed and dispatched for Clock set/get and Power domain (PSC) enable/disable

4. ATF processes the request and sends the response back through the same shared memory.

5. The application reads the result after the SMC returns.

Suggested Files to Review:

To understand the full flow of set_clock, get_clock, and psc enablement:

• Start from the SCMI protocol layer in the code.

• Trace the flow through the platform-specific service handlers.

• From there, the call goes into internal clock/PSC driver layers (not a single API, it’s a chained call flow).

The codes below are on the ATF side, so when the SCMI call requests based on the set or get or psc enabled, the ATF calls the particular API.

Regards,

Anil.