Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi Team,

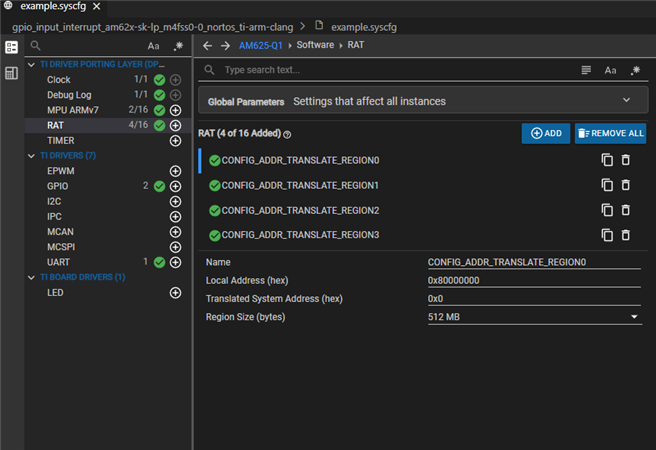

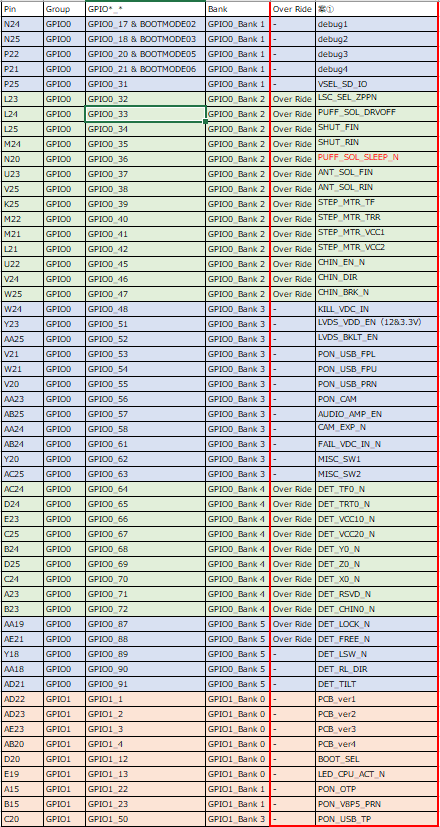

Is it possible to configure the RAT in sysconfig for a specific GPIO bank? They specifically want to configure for the pins marked as over ride as listed below in the table.

Best regards,

Mari Tsunoda