Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

We have new design request TWO MCSPI ports, how to configure UDMA for each MCSPI port, I know how to configure a UDMA to one MCSPI port. below is my code for configure one MCSPI port, the Udma_init() seems can be called once, but how do I create one more UDMA for second SPI?

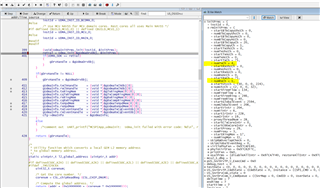

Udma_DrvHandle MCSPIApp_udmaInit(SPI_v1_HWAttrs *cfg)

{

int32_t retVal = UDMA_SOK;

Udma_InitPrms initPrms;

uint32_t instId;

if (gDrvHandle == NULL) /* PRQA S 2991, 2994 */

{

/* UDMA driver init */

#if defined (SOC_AM64X)

/* Use Block Copy DMA instance for AM64x */

instId = UDMA_INST_ID_BCDMA_0;

#else

/* Use MCU NAVSS for MCU domain cores. Rest cores all uses Main NAVSS */

#if defined (BUILD_MCU1_0) || defined (BUILD_MCU1_1)

instId = UDMA_INST_ID_MCU_0;

#else

instId = UDMA_INST_ID_MAIN_0;

#endif

#endif

(void)UdmaInitPrms_init(instId, &initPrms);

retVal = Udma_init(&gUdmaDrvObj, &initPrms);

if(UDMA_SOK == retVal)

{

gDrvHandle = &gUdmaDrvObj;

}

}

if(gDrvHandle != NULL)

{

gDrvHandle = &gUdmaDrvObj;

gUdmaInfo.txChHandle = (void *)&gUdmaTxChObj;

gUdmaInfo.rxChHandle = (void *)&gUdmaRxChObj;

gUdmaInfo.txRingMem = (void *)&gTxRingMem[0];

gUdmaInfo.cqTxRingMem = (void *)&gTxCompRingMem[0];

gUdmaInfo.rxRingMem = (void *)&gRxRingMem[0];

gUdmaInfo.cqRxRingMem = (void *)&gRxCompRingMem[0];

gUdmaInfo.txHpdMem = (void *)&gUdmaTxHpdMem[0];

gUdmaInfo.rxHpdMem = (void *)&gUdmaRxHpdMem[0];

gUdmaInfo.txEventHandle = (void *)&gUdmaTxCqEventObj;

gUdmaInfo.rxEventHandle = (void *)&gUdmaRxCqEventObj;

cfg->dmaInfo = &gUdmaInfo;

}

else

{

/* UART_printf("MCSPIApp_udmaInit: Udma_init failed with error code: %d\n", retVal); */

}

return (gDrvHandle);

}

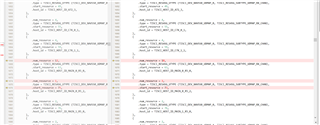

SPI_HWAttrs spi_cfg =

{

.baseAddr = CSL_MCSPI0_CFG_BASE,

.intNum = CSLR_MAIN2MCU_LVL_INTRTR0_IN_MCSPI0_INTR_SPI_0,

.pinMode = (uint32_t)SPI_PINMODE_4_PIN,

.chNum = MCSPI_CHANNEL_0,

// .chMode = MCSPI_SINGLE_CH,

.chMode = MCSPI_MULTI_CH,

.enableIntr = (bool)ME_FALSE,

.inputClkFreq = 48000000U,

.initDelay = MCSPI_INITDLY_0,

.rxTrigLvl = MCSPI_RX_TX_FIFO_SIZE,

.txTrigLvl = MCSPI_RX_TX_FIFO_SIZE,

.chnCfg =

{

[0] =

{

.csPolarity = MCSPI_CS_POL_LOW,

.dataLineCommMode = MCSPI_DATA_LINE_COMM_MODE_7,

.tcs = MCSPI_CH0CONF_TCS0_ZEROCYCLEDLY,

.trMode = MCSPI_TX_RX_MODE,

},

[1] =

{

.csPolarity = MCSPI_CS_POL_LOW,

.dataLineCommMode = MCSPI_DATA_LINE_COMM_MODE_7,

.tcs = MCSPI_CH1CONF_TCS1_ZEROCYCLEDLY,

.trMode = MCSPI_TX_RX_MODE,

},

},

.rxDmaEventNumber = CSL_PDMA_CH_MAIN_MCSPI0_CH0_RX,

.txDmaEventNumber = CSL_PDMA_CH_MAIN_MCSPI0_CH0_TX,

};

spi_cfg.edmaHandle = (void *)MCSPIApp_udmaInit(&spi_cfg);

spi_cfg.dmaMode = (bool)TRUE;