Tool/software:

Hi Team,

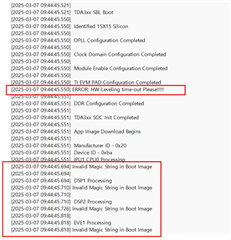

My customer has some issue while they are using TDA3MVRBFABFRQ1

with 2pcs DDR3(K4B4G1646E-BNCB)

Here's the log they get.

What can be the cause of this problem?

if you need more data to analyze this please let me know.

Regards,

Ted